The National Security Agency's review of emerging technologies

ISSN 2640-1789 (Print) | ISSN 2640-1797 (Online)

NEXT-GENERATION HARDWARE FOR HIGH-PERFORMANCE COMPUTING

# **Editors' column**

David J. Mountain & Robert J. Runser

# It's not only merely dead, it's really most sincerely dead.

~Computer engineer who shall remain anonymous~

A brilliant observation by Gordon Moore in 1965 [1], and a precise technical analysis by Robert Dennard et al. in 1974 [2], paved the way for multiple decades of general purpose computing advancements by following one straightforward imperative—make transistors smaller. Consider this comparison:

- In 1971, Intel developed the 4004 microprocessor, which had a 4 bit data path, 740 kilohertz clock, and was fabricated on 10 micron technology.

- By 2005, Intel's Pentium microprocessor had a 64 bit data path, 3.8 gigahertz clock, and was fabricated on 0.09 micron technology.

That's an 80,000-times improvement in raw compute capability—a 40 percent increase per year—primarily driven by a reduction in transistor area of 12,000 times. This one rising tide lifted all boats, enabling computers as a general purpose technology to become ubiquitous in business, personal, and public sectors.

Alas, no exponential can continue forever; since early in the 21st century, a variety of issues, both technical (i.e., power dissipation, leakage currents, on-chip wire resistance) and non-technical (i.e., rising costs of fab facilities and masks, manufacturing and chip design complexity), have greatly eroded the value of complementary metal-oxide-semiconductor (CMOS) transistor scaling in improving computers. Fundamental research into new materials, novel architectures, and new domains for computation will drive advances in the years to come. These advances will be less predictable, require a greater diversity of solutions, and will demand highly creative ideas from the research community. NSA Research is an active participant, deeply involved in a wide variety of explorations, understanding and shaping the next wave of computing technology. We present some of our work in this special issue on computing hardware.

We start this issue with a look at the most basic technology for computing—materials. In "Beyond silicon: Novel materials heterostructures for future high-performance computing," Adam Friedman et al. describe an exciting array of novel materials and devices based on unique properties created by two-dimensional or topological effects that use spintronic, photonic, and magnetic effects to manipulate information.

In "Optical coprocessor generates bright future for probabilistic computing," John T. Daly moves up the computing stack to a functional design, describing how inherent properties of optics can be combined with mathematical techniques to perform multiplications. The emergence of nanoscale optics is examined as a path toward practical use of these ideas.

Probabilistic processing is further explored in "The Ising machine—A probabilistic processing-in-memory computer," by Lauren Huckaba. The basic Ising model

<sup>[1]</sup> Moore GE. "Cramming more components onto integrated circuits." Electronics. 1965;38(8). Available at: https://newsroom.intel.com/wp-content/ uploads/sites/11/2018/05/moores-law-electronics.pdf.

<sup>[2]</sup> Dennard RH, Gaensslen FH, Yu H, Rideout VL, Bassous E, LeBlanc AR. "Design of ion-implanted MOSFETs with very small physical dimensions." IEEE Journal of Solid-State Circuits. 1974;9(5):256-268. Available at: https://doi.org/10.1109/JSSC.1974.1050511.

and Ising problem are described, followed by a description of how coupled oscillator systems can be configured to solve optimization problems of interest.

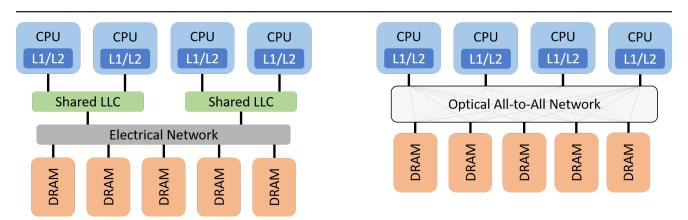

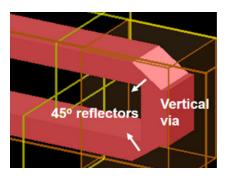

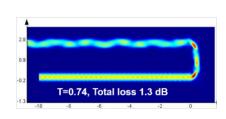

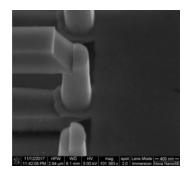

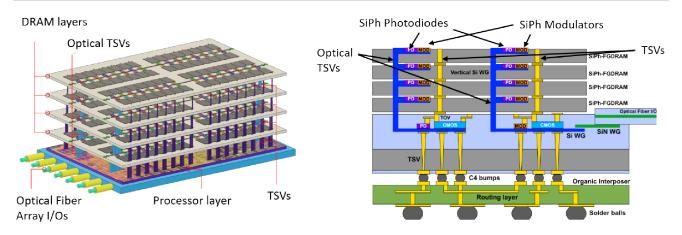

We return to nanophotonics technology in "Cacheless computer architectures: 3D integration of optical interconnects and novel memory," by Eric Cheng and S. J. Ben Yoo. Cleverly combining the technologies of silicon photonics, low-latency memory, and optical vias for vertical packaging is shown to be highly advantageous for high-performance data analytics.

Continuing our focus on applications, Roger Pearce and Geoffrey Sanders describe how exploratory data analytics can be deployed at unprecedented scale by using new solid-state devices in "Persistent memory as the substrate for HPC-scale graph analytics."

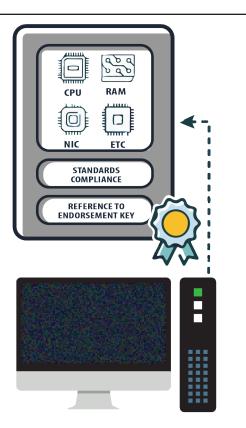

Our final article, "Hardening the hardware supply chain: Standardized artifacts enable automated accountability" by Andrew Medak, reminds us of the need for supply chain security, and provides a model for how that can be accomplished even when vulnerabilities exist at many points along the way.

We thank the authors for their fantastic work and their willingness to provide a partial glimpse into NSA Research. We also want to thank Jessica for her efforts in "herding the technical cats" and bringing this issue into print. We hope you enjoy this issue of *The Next Wave*, and welcome aboard!

### David J. Mountain

Advanced Computing Systems Research Directorate, NSA

**Robert J. Runser** Technical Director Research Directorate, NSA

### **Contents**

2 Beyond Silicon: Novel Materials Heterostructures for Future High-Performance Computing

Adam L. Friedman, Aubrey T. Hanbicki, Jennifer E. DeMell, Nicholas A. Blumenschein, Gregory M. Stephen

- 12 Optical Coprocessor Generates Bright Future for Probabilistic Computing

JOHN T. DALY

- 19 The Ising Machine—A Probabilistic Processing-in-Memory Computer

Lauren Huckaba

- 27 Cacheless Computer Architectures: 3D Integration of Optical Interconnects and Novel Memory

ERIC CHENG, S. J. BEN YOO

33 Persistent Memory as the Substrate for HPC-Scale Graph Analytics

ROGER PEARCE, GEOFFREY SANDERS

40 Hardening the Hardware Supply Chain: Standardized Artifacts Enable Automated Accountability

Andrew Medak

The Next Wave is published to disseminate technical advancements and research activities in telecommunications and information technologies. Mentions of company names or commercial products do not imply endorsement by the US Government. The views and opinions expressed herein are those of the authors and do not necessarily reflect those of the NSA/CSS.

This publication is available online at <a href="http://www.nsa.gov/thenextwave">http://www.nsa.gov/thenextwave</a>. For more information, please contact <a href="jsmarx@uwe.nsa.gov">jsmarx@uwe.nsa.gov</a>.

ISSN 2640-1789 (Print) ISSN 2640-1797 (Online)

or the last 75 years, the operation of the majority of electronics has been based on manipulating electron charge in the elemental semiconductor silicon. The basic device operation of the silicon transistor is referred to as complementary metal-oxidesemiconductor (CMOS). While this paradigm was amazingly successful for generations, CMOS is reaching its physical limits and will be unable to keep pace with the speed, energy, and size requirements critical for data manipulation and the storage needs of the commercial, defense, and intelligence communities. Research into the next generation of materials and devices is therefore essential to enable future high-performance computing (HPC) platforms.

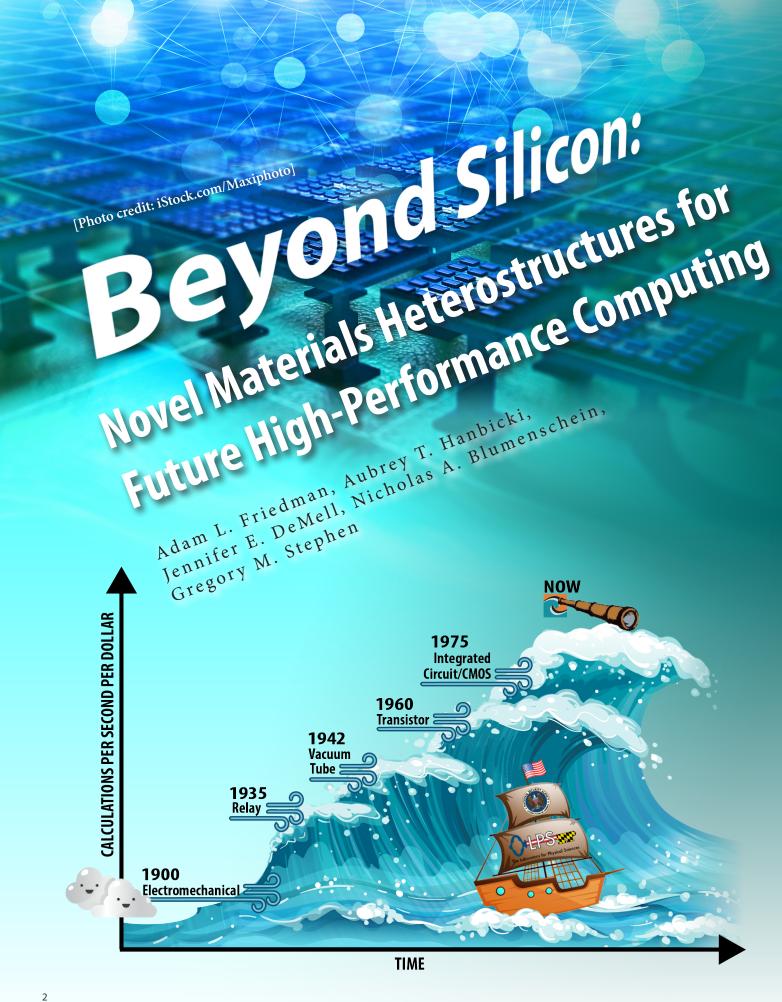

Consider that technologies are like waves (as in figure 1)—they slowly build up and then eventually crest while a new wave builds—a suitable analogy for this publication. Moore's law, the empirical observation that the number of transistors on a chip doubles approximately every two years, is the defacto driving force behind the current wave and has resulted in exponential growth in computing power. Troublingly, no new wave has been clearly identified. Without a firm path beyond the current paradigm—the Next Wave—critical computing needs will not be met.

### **Background**

To enable future HPC systems, we need to imagine and create innovative solutions to fuel the next wave. This includes developing devices that incorporate alternate-state variables, for example, electron spin (i.e., spintronics), magnetism, or photonic devices that utilize inherent material properties besides electron charge to manipulate information. Ultimately, a "materials-by-design" solution will be feasible by combining

FIGURE 1. The waves of technology from 1900 to now are much like waves in an ocean. A new wave increases the total calculations per second per dollar with each new technology. The wave builds up slowly, then quickly gains momentum and takes over, finally cresting while a new wave begins building. There is no clear next wave on the horizon. Technology users ride the waves like boats in the ocean. Researchers work to identify new waves before the prior waves crash onto them.

different materials to create the necessary properties. Beyond the development of new devices, the entire advanced computing system problem space—material, device, architecture, etc.— must be holistically considered, a concept referred to as codesign.

Research into alternate-state variables, coupled with breakthroughs in materials science that include entirely new materials classes with a host of advantageous properties, is generating a considerable

amount of excitement in the HPC field for novel materials and devices. In particular, devices fabricated from novel two-dimensional (2D) materials, topological Dirac materials, or novel magnetic materials are expected to offer an avenue for lower-power, higher-performance memory and logic beyond Moore's law [1, 2]. However, basic research must be performed to identify the best materials and alternate-state variables to use from the available new classes. In addition, we must better understand how to make usable devices with combinations of these materials that optimize properties and solutions.

The Laboratory for Physical Sciences (LPS) has a novel materials and devices research program, and our objective in this program is to explore the properties of devices that incorporate emerging materials such as topological Dirac materials, 2D materials, and magnetic-phase-change materials with a goal of creating better capabilities (e.g., faster speed, lower-power, greater versatility/functionality) for memory, logic, and HPC beyond the paradigms established by Moore's law. This requires high-risk, high-reward research that is focused on understanding the unknown basic properties of promising new materials, determining exactly which properties can be exploited to the greatest effect, and designing, fabricating, and

testing devices that use these properties and that can be quickly transitioned into technologies with the potential for disruptive, non-incremental discovery and implementation. In this article, we will briefly discuss two recent prototype devices developed at LPS: topologically enabled spintronic devices further exemplified by a cadmium arsenide (Cd<sub>3</sub>As<sub>2</sub>)/fluorographene heterostructure non-local spin valve, and a metamagnetic iron rhodium (FeRh) memory element.

### **Topologically enabled electronics**

Topological materials have special properties enabled by their physical structure, or topology. Topological Dirac materials, a recently discovered class of materials, have the potential to enable spintronics as the defining technology of future electronic systems [3]. In these materials, the conduction and valence energy bands meet at a single "Dirac point," resulting in a host of exciting properties such as relativistic electronic transport and dissipationless spin transport.

The most well-known Dirac material is graphene, a 2D version of graphite. Another is bismuth selenide (Bi<sub>2</sub>Se<sub>3</sub>), a so-called topological insulator because only its surface conducts electricity [4]. Another promising new material is Cd<sub>3</sub>As<sub>2</sub>, which is a topological Dirac semimetal (TDS). This material can be tuned between multiple quantum phases (QPs), allowing for a truly multifunctional material [5]. While CMOS relies on toggling between charge states, a system made with Cd<sub>3</sub>As<sub>2</sub> devices could reversibly switch between computing modes by toggling between the QPs—a process that is both faster and lower energy, while at the same time allowing inherent reprogrammability and multifunctionality.

In a recent, exciting agency first, LPS received funding support from the Office of the Under Secretary of Defense, Research & Engineering as part of an Applied Research for the Advancement of Science and Technology Priorities (ARAP) program in collaboration with the Army Research Laboratory, Naval Research Laboratory, and the Air Force Research Laboratory. The purpose of the program is to design, fabricate, and prototype new Dirac material/topological memory and logic devices with technologically disruptive potential. Two identified pathways are through

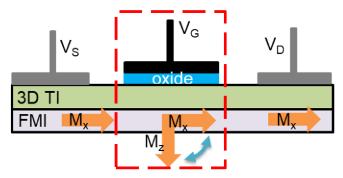

topological magnetoelectronic (TMET) logic and with magnetic topological memory (MTM).

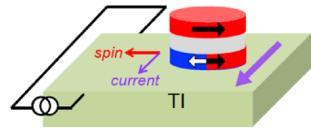

The TMET project is concentrated on a device that works by using an external electric field to toggle the direction of a magnetic field in close proximity to a topological Dirac material, thereby using the magnetic interaction to switch a transistor-like device ON or OFF. This quantum transistor would operate at 1,000 times less power and 10 to 1,000 times faster speeds than today's state of the art. The MTM device operates by exploiting a unique property of a topological Dirac material—its spin is locked to its momentum. Using a process called spin-orbit-torque (SOT) to change the magnetic moment of an element, called a magnetic tunnel junction (MTJ), it provides the same functionality as commercial magnetoresistive random-access memory (MRAM). However, SOT-MTJs are significantly faster and use a fraction of the energy compared to commercial MRAM. The charts in figure 2 summarize the ARAP technologies.

For topologically enabled devices to become reality, we first must better understand the fundamental behavior of the materials. For example, how long does it take spins to scatter? How efficient is the spin-charge conversion? Recently, LPS was one of the first to answer these questions by investigating the spin Hall effect (SHE) in topological Dirac materials using a method previously used to investigate atomically heavy metallic materials. The SHE occurs when a charge current passes through a material with a high spin-orbit coupling (like a topological material), which functionally acts as an internal magnetic field, thereby producing a perpendicular spin current. The effect is reversable: a spin current also produces an orthogonal charge current via the inverse spin Hall effect (ISHE).

Thus, the SHE and ISHE directly measure how efficiently a material converts charge currents into spin currents and vice versa. In addition, these measurements can also tell us the spin diffusion length and spin relaxation time, which are measures of how far the spin travels before it scatters and how much time elapses between scattering events. A more robust spin current will directly lead to more robust information manipulation in future devices.

### (a) Topological Logic

### (b) Topological Memory

| PROPERTY                                    | HIGH-<br>PERFORMANCE<br>CMOS                                    | TMET                                                                                                           | PROPERTY                               | CMOS NVM<br>(E.G., FLASH,<br>STT MRAM)                            | TOPOLOGICAL<br>MRAM                                                                   |

|---------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Subthreshold<br>slope                       | Typical: 70mV/dec Theoretical min @ RT: 60mV/dec                | 0.7–40mV/dec (Value limited by magnetism, not temp)                                                            | Bit-switch<br>energy cost              | 10° J                                                             | 10 <sup>-18</sup> –10 <sup>-15</sup> J                                                |

| Operational<br>power loss per<br>32-bit ALU | 0.1 mW                                                          | 1 μW                                                                                                           | Switching speed (RAM is > 1 GHz)       | 100–1000 MHz<br>Only USB<br>storage                               | 1–10 GHz Ferromagnet  1 THz antiferromagnet  Operable as RAN                          |

| Device<br>optimization                      | Reaching limits<br>of engineering<br>(e.g., FinFet,<br>Chiplet) | New parameter<br>space to optimize<br>Structural device<br>optimizations are<br>transferable (e.g.,<br>FinFet) | Power<br>dissipation if<br>used as RAM | 0.1–1 W/bit                                                       | 10–10 <sup>4</sup> nW/bit                                                             |

| High-<br>frequency<br>response              | Requires<br>complex HEMT<br>material stacks                     | Naturally high-<br>mobility channels                                                                           | Industrial<br>maturity                 | End of Moore.<br>Seventy years of<br>advancements<br>nearing end. | Non-topological<br>MRAM<br>Shipped in 2016<br>(Everspin)<br>(Everspin, 1 Gb,<br>2019) |

FIGURE 2. (a) In this schematic of the topological magnetoelectronic transistor (TMET) device, a 3D topological insulator Dirac material (3D TI) sits on a ferromagnetic insulator (FMI) with a magnetic moment that toggled using an oxide gate (red dotted line). The device toggled on/off by switching the direction of the magnetic moment in the FMI. The advantages are indicated in the chart by color: red fails to meet future requirements, yellow barely meets future requirements, and green fully meets future requirements. (b) In this schematic of the magnetic topological memory device, a charge current in a topological Dirac material is naturally transduced into a spin current. The spin current interacts with a magnet that is a layer in a magnetic tunnel junction (MTJ). MTJs are created by sandwiching an insulating material between two ferromagnetic materials. When the magnetic moments of the two ferromagnetic nets are parallel/antiparallel, the resistance is low/high. The resistance state is written or read depending on the applied current. The advantages are indicated in the chart by color.

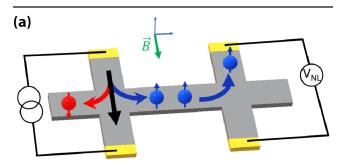

The SHE and ISHE measurements are performed as shown in figure 3. This geometry, called a Hall bar, is the basis for a wide variety of electronic measurements. When a conventional charge current passes between one set of side contacts (left), it produces a spin current in the central channel via the SHE. When this subsequent spin current reaches a second set of contacts (right), the spin current converts back into a charge current via the ISHE. Because the circuit does not directly connect these two sets of contacts, the resulting charge current in the contacts on the right manifests as a voltage. By applying a magnetic field along the initial charge current path, we can disrupt the flow of spins and measure the resulting effect on the voltage. The applied field causes the spins to precess, or rotate around an axis, reducing the measured voltage as a decaying oscillatory function of the applied field [6]. The voltage decrease is directly proportional to the spin-charge conversion efficiency of the material, and its decay gives us the spin diffusion length and spin relaxation time.

Metals like platinum (Pt) and tungsten (W) are currently used in spin-orbit torque-based MRAM designs and have spin-charge conversion efficiencies on the order of 0.05-0.1. The efficiency for topological materials can be more than 10 times larger. The topological insulator bismuth antimony (Bi<sub>0.9</sub>Sb<sub>0.1</sub>) has an efficiency as high as 52 [7]. The efficiency is directly proportional to the current required to switch a bit: 10 times higher spin efficiency will result in 10 times less needed current and therefore 10 times less power. The spin diffusion length and relaxation time gives limits on the speed and dimensions of the devices, as any manipulation of the spins must occur before the spin information disappears. Based on these measurements, we can begin to select materials that optimize our device designs.

# Cd<sub>3</sub>As<sub>2</sub>/Graphene spin valves: A novel topological Dirac material/2D heterostructure

Cd<sub>3</sub>As<sub>2</sub> is an excellent candidate for topologically enabled electronics. Cd<sub>3</sub>As<sub>2</sub> has a tunable quantum phase, a high mobility, microns-long spin diffusion lengths, and high spin-charge conversion efficiency. We have also identified a 2D material, fluorographene, as an excellent material to use to couple to the Cd<sub>3</sub>As<sub>2</sub> to build a spintronic heterostructure. We want to combine these materials because when disparate materials

(e.g., Dirac materials, 2D materials, and novel magnetic materials) form heterostructures, the individual properties of each material can overlap due to atomic-level proximity. As an example of how powerful this

**FIGURE 3. (a)** This schematic of a spin Hall effect (SHE) device shows a charge current flowing through the contacts on the left, which generates a spin current. When the spin current reaches a second set of contacts outside of the charge current path (on the right of the schematic), it creates a measurable voltage. **(b)** This optical image is of a topological SHE device. (R<sub>NL</sub> stands for non-local resistance.) **(c)** When a magnetic field is applied in plane, the spins begin to precess. Sweeping the field causes dephasing (black dotted curve). The data are fit to a model (red line) and important parameters can be extracted.

technique can be, consider a stack of 2D materials. These are single layer sheets ranging from one to five atoms thick, are mechanically flexible, can be grown in large areas, and can have various electronic states (e.g., semiconductor, metal, semimetal, superconductor, insulator, etc.). They are discretely stackable so they can be used to create true materials by design, where the final bulk heterostructure contains material properties made to order [8]. Two layers of graphene, atomically thin layers of carbon atoms, can be stacked on top of each other and, depending on the relative angle between them, can be insulating, metallic, or even superconducting.

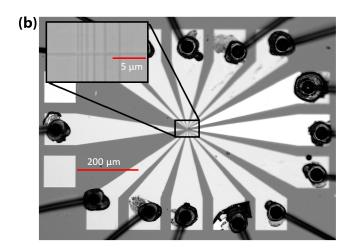

The fundamental spintronic device is the nonlocal spin valve (NLSV). Here, spin current in a channel is compared to a magnet moment in a detector contact. Depending on the relative orientation of the contact with the injected spin moment, there will be a highor low-magnitude resistance in the device. Figure 4 shows an optical image of a NLSV along with a schematic representation. Two tunneling ferromagnetic contacts (center lines, fluorographene/magnesium oxide (MgO)/Permalloy (Py) are placed on top of a spin-transport channel, in this case Cd<sub>2</sub>As<sub>2</sub>[9]. Py is a magnetic alloy containing 80 percent nickel and 20 percent iron.

The spintronic behavior of the NLSV is entirely enabled by the fluorographene/MgO tunnel barrier. Electronic tunneling is a quantum mechanical effect occurring when electrons "tunnel" or pass through materials that classically should block them. As an analogy, one can think of a ball thrown at a brick wall. Classically, the ball will bounce back. However, quantum mechanically, the ball will occasionally go through and come out on the other side. For the NLSVs, this barrier is essential due to the electronic properties of the ferromagnet (FM) and the spin channel. The FM is a normal metal, but the spin channel is a semimetal; it conducts current but far less efficiently than the FM. Without the tunnel barrier, the spin channel could not handle the number of electrons trying to move through it, so they bounce off the interface and interfere with the ones that do get through. The tunnel barrier acts as a sort of flow regulator, limiting the number of electrons that get through and allowing for a much smoother flow of electrons into the device.

Graphene makes an excellent tunnel barrier due to its 2D nature. Graphene is conductive in-plane,

but highly resistive out-of-plane. It can be discretely stacked (at 0.3 nanometers thick!) onto any surface, is self-healing, is pinhole free, and can further serve

FIGURE 4. (a) In this optical image of a Cd<sub>3</sub>As<sub>3</sub>/fluorographene non-local spin valve, current flows between the nonmagnetic titanium/gold (Ti/Au) reference contact and the fluorographene/ MgO/Py/Au ferromagnetic tunneling contact as shown on the left side of the device. A non-local voltage measured due to a pure spin current is then measured between a second set of similar contacts on the right of the device. (b) In this illustration, the fluorographene/MgO/Py/Au contacts are different widths to exploit shape anisotropy, allowing the magnetic moments in the contacts to switch at different fields, leading to the resistance states seen in the inset of (c) where the green arrows indicate a low/high magnitude resistance state when the relative magnetic moment orientations are parallel/antiparallel. The black/red curve in the inset is for sweeping the magnetic field from negative/positive to positive/negative. The magnitude of the resistance change is measured as  $\Delta R_{_{\text{NI}}}$  . The inset is at room temperature as indicated in the large curve of (c).

as a chemical diffusion barrier to prevent oxidation and unwanted alloying. Additionally, it can be grown in large area sheets inexpensively in a simple furnace reactor [ $\underline{10}$ ]. When graphene is exposed to xenon difluoride ( $XeF_2$ ) gas, the fluorine ions bond to the graphene surface to create fluorographene. This layer is completely insulating and serves as an atomically thin barrier between the FM and the spin channel.

As a charge current passes from a FM contact, through the tunnel barrier, into the Cd, As, channel and out of a reference contact [titanium/gold (Ti/Au)], a spin current is also produced that radiates outward. Because the spin current travels in all directions, unlike the charge current, it is detected in the second set of FM/Au contacts. The measured electrical resistance at the second FM will be higher when the magnetic moments of the two FMs are antiparallel compared to when they are parallel, giving the HIGH and LOW states necessary for digital memory. The magnetic moments are switched using an external magnet as described in the caption of figure 4. Alternatively, the spin current simply toggles on and off by decreasing the spin relaxation time in the channel using, for example, a gate voltage, allowing logic operations with the same device.

Recently we demonstrated high-quality spintronic switching in a Cd<sub>3</sub>As<sub>2</sub>/graphene NLSV heterostructure device from cryogenic temperatures up to room temperature. Our devices, the first NLSVs to utilize Cd<sub>3</sub>As<sub>2</sub>, operate with a 10 times larger signal than silicon-based devices. Moreover, this is just the first step. Our ongoing research includes controlling the quantum phase of the Cd<sub>3</sub>As<sub>2</sub> in the device by changing the channel thickness, applying an electric field through external gating, or atomically doping the Cd<sub>3</sub>As<sub>2</sub> films.

### Metamagnetic iron rhodium

Another possible way to improve spintronic switching behavior and realize next-generation topologically enabled logic or memory elements is to incorporate ferromagnets that are more complex with greater functionality and improved material properties. One material of particular interest is FeRh. FeRh possesses a temperature-dependent metamagnetic phase change where it transitions from antiferromagnetic to ferromagnetic (AFM-FM) with increasing temperature [11]. The temperature at which this transition occurs

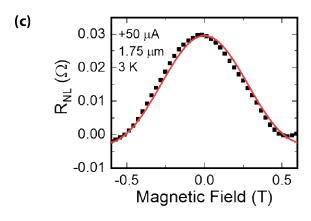

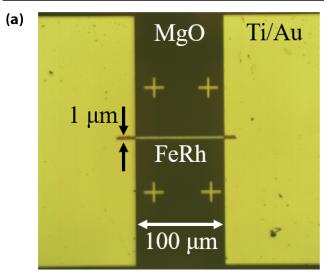

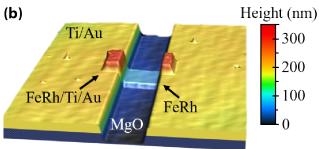

**FIGURE 5. (a)** This diagram is a top-view optical image of the fabricated device with FeRh wire width and length of 1 micrometer (μm) and 100 μm, respectively, and **(b)** is a 3D optical image of the device. **(c)** This graph shows the resistance measurement while varying the ambient temperature from 320–450 K. Red and blue curves represent heating and cooling cycles, respectively. Background shading colors denote temperature regimes at which the FeRh is antiferromagnetic (AFM, blue), ferromagnetic (FM, red), and in transition (white).

$(T_{cr})$ , can be fine-tuned using various fabrication techniques, such as substitutional doping [12] and patterning [13]. According to Pouillet's law, expansion of a unit cell will naturally cause its electrical resistance to decrease for a given length of material. Therefore, by careful manipulation of temperature, both the magnetic state and electrical resistance can be selected, allowing its use in switching device applications. This becomes even more attractive when considering the 350 femtosecond AFM-FM transition time, translating to an operating frequency of nearly 3 terahertz [14].

Optical images of simple FeRh devices that we fabricated by standard lithographic methods are shown in figures 5(a) and (b). The simplicity of fabrication is another advantage of working with FeRh. Figure 5(c) demonstrates the AFM-FM transition. The measurement begins at a starting temperature of 320 kelvins (K). Upon increasing the temperature (red curve), the wire resistance also increases. The AFM-FM transition begins once the FeRh temperature surpasses 365 K, accompanied by a decreasing resistance. The effect persists until the temperature reaches 420 K, indicating that the wire has fully transitioned into the ferromagnetic phase. The opposite effect occurs when cooling the wire (blue curve).

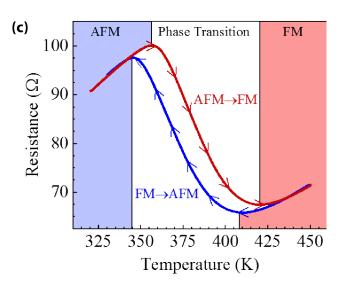

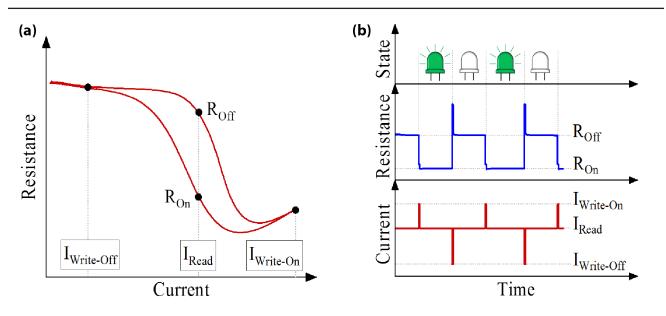

To make a useful device, the state must be controlled via current rather than temperature. According to the Joule-Lenz law, an electrical current through the wire will cause the FeRh temperature to increase until it thermally stabilizes. In figure 6(a), a pulsed current controls the temperature. The FeRh temperature and subsequent resistance are held to a constant value by a constant current (I<sub>Read</sub>). Here, the FeRh will remain in the high-resistance AFM phase (OFF state). If the current amplitude is sufficiently increased, the wire temperature will rise past T<sub>Cr</sub> and the FeRh will transition into the low-resistance ferromagnetic phase (ON state). As shown previously, the FeRh will remain in the ferromagnetic phase until cooled to below T<sub>c</sub>. Therefore, applying a continuous current  $(I_{Read})$  will maintain the present state of the device. Upon reducing the current, the FeRh transitions back into the high-resistance antiferromagnetic phase (OFF state). In figure 6(b), a pulsed current switches the FeRh back-and-forth between antiferromagnetic (OFF) and ferromagnetic (ON) states.

One possible application of a device with this hysteretic behavior is as a memristor, the basic memory component of many neuromorphic circuit designs. The device demonstrated here uses the magnetization

FIGURE 6. (a) This graph shows FeRh resistance as a function of current. Joule heating changes the wire temperature and subsequent phase, allowing for antiferromagnetic and ferromagnetic state control via electrical bias. A constant current I<sub>Read</sub> will allow the FeRh temperature to stabilize. An FeRh transition is made with a short current pulse of I<sub>Write-Off</sub> or I<sub></sub> resistance and current profiles as a function of time. Repetitively switching between pulse current amplitudes of  $I_{Write-On}$  and  $I_{Write-Off}$ causes FeRh phase transitions and substantial change in the wire resistance. The green bulbs represent the ON state

of the material as a state variable, which inherently provides reproducibility, endurance, and state retention in comparison to charge-based switching devices. The switching capability of these devices is estimated to be on the order of 1 picosecond [14]. For comparison, previously reported devices with more advanced architectures have switching times that range from 50 nanoseconds to more than 100 microseconds [15, 16]. Moreover, one could imagine incorporating a metamagnetic element into the previously described NLSV. The metamagnetic transition would switch off the spin current in the NLSV, thereby allowing transistor-like behavior. Alternatively, the metamagnetic transition could switch the device into a new operational mode.

# Conclusion and a beginning: Vision for the future

Moore's law began as an observation of the density of transistors in a circuit. Serving as a roadmap for the entire semiconductor industry, it has subsequently transformed into a self-fulfilling prophecy. It has been re-imagined, re-invented, and ultimately embraced as a mindset, an approach, and a philosophy. Device scientists and engineers have accomplished everything envisioned by Gordon Moore in 1965 [17] and are quickly approaching the physical limits which portend an end to this path.

One possible path toward a new scientific paradigm can be found by going back in history to even before the 1965 observation by Moore. Richard Feynman, in his famous speech "There's plenty of room at the bottom" [18], given at the American Physical Society meeting in December 1959, is often credited with inventing the field of nanoscience. He revisited and repurposed a similar line of reasoning in a 1983 speech given at the Jet Propulsion Laboratory and, astonishingly, established the field of quantum computing [19]. Although his prophesies do not specify a pathway to advanced classical HPC, Feynman does establish a way forward by suggesting a holistic, outward-looking approach to device (co-)design. Summarizing this approach, Feynman said, "It would be interesting in surgery if you could swallow the surgeon" [18].

The novel materials and devices that we described here present the beginning of a new era in computing technologies. In his address to the American Physical Society, Feynman said:

What could we do with layered structures with just the right layers? What would the properties of materials be if we could really arrange the atoms the way we want them?... I can't see exactly what would happen, but I can hardly doubt that when we have some control of the arrangement of things on a small scale we will get an enormously greater range of possible properties that substances can have, and of different things that we can do.

Indeed, by choosing the best materials and combining them in new ways with operating modes in mind, we can optimize our future computing systems and maintain a critical quantitative edge for the future.

### References

- [1] Pesin D, MacDonald AH. "Spintronics and pseudospintronics in graphene and topological insulators." *Nature Materials*. 2012;11:409–416. Available at: <a href="https://doi.org/10.1038/nmat3305">https://doi.org/10.1038/nmat3305</a>.

- [2] IEEE. The International Roadmap for Devices and Semiconductors. 2020. Available at: <a href="https://irds.ieee.org/editions/2020">https://irds.ieee.org/editions/2020</a>.

- [3] Wang XL. "Dirac spin-gapless semiconductors: Promising platforms for massless and dissipationless spintronics and new (quantum) anomalous spin Hall effects." *National Science Review.* 2017;4(2):252–257. Available at: <a href="https://doi.org/10.1093/nsr/nww069">https://doi.org/10.1093/nsr/nww069</a>.

- [4] Jamali M, Lee JS, Jeong JS, Mahfouzill F, Lv Y, Zhao Z, Nikolić BK, Mkhoyan KA, Samarth N, Wang JP. "Giant spin pumping and inverse spin Hall effect in the presence of surface and bulk spin–orbit coupling of topological insulator Bi<sub>2</sub>Se<sub>3</sub>." *Nano Letters.* 2015;15(10):7126–7132. Available at: <a href="https://doi.org/10.1021/acs.nanolett.5b03274">https://doi.org/10.1021/acs.nanolett.5b03274</a>.

- [5] Goyal M, Galletti L, Salmani-Rezaie S, Schumann T, Kealhofer DA, Stemmer S. "Thickness dependence of the quantum Hall effect in films of the three-dimensional Dirac semimetal Cd<sub>3</sub>As<sub>2</sub>" *APL Materials.* 2018;6(2):026105. Available at: <a href="https://doi.org/10.1063/1.5016866">https://doi.org/10.1063/1.5016866</a>.

- [6] Abanin DA, Shytov AV, Levitov LS, Halperin BI. "Nonlocal charge transport mediated by spin diffusion in the spin Hall effect regime." Physics Review B. 2009;79(3):035304. Available at: https://doi.org/10.1103/PhysRevB.79.035304.

- [7] Khang NHD, Ueda Y, Hai PN. "A conductive topological insulator with large spin Hall effect for ultralow power spinorbit torque switching." Nature Materials. 2018;17:808-813. Available at: <a href="https://doi.org/10.1038/s41563-018-0137-y">https://doi.org/10.1038/s41563-018-0137-y</a>.

- [8] Friedman AL, Hanbicki AT, Perkins FK, Jernigan GG, Culbertson JC, Campbell PM. "Evidence for chemical vapor induced 2H to 1T phase transition in MoX, (X = Se, S) transition metal dichalcogenide Films." *Scientific* Reports. 2017;7:3836. Available at: https://doi.org/10.1038/ <u>s41598-017-04224-4</u>.

- [9] Stephen GM, Hanbicki AT, Schumann T, Robinson JT, Goyal M, Stemmer S, Friedman AL. "Room-temperature spin transport in  $Cd_3As_2$ ." ACS Nano. 2021;15(3):5459–5466. Available at: <a href="https://doi.org/10.1021/acsnano.1c00154">https://doi.org/10.1021/acsnano.1c00154</a>.

- [10] Bae S, Kim H, Lee Y, Xu X, Park JS, Zheng Y, Balakrishnan J, Lei T, Kim HR, Song Y, Kim Y, Kim KS, Özyilmaz B, Ahn J, Hong BH, Iijima S. "Roll-to-roll production of 30-inch graphene films for transparent electrodes." *Nature Nanotechnology.* 2010;5:574–578. Available at: <a href="https://doi.">https://doi.</a> org/10.1038/nnano.2010.132.

- [11] Fallot M, Hocart R. "Sur l'apparition du ferromagnetisme par elevation de temperature dans des alliages de fr et de rhodium." La Rev. Sci. 1939;77:3.

- [12] Le Graët C, Charlton TR, McLaren M, Loving M, Morley SA, Kinane CJ, Brydson RMD, Lewis LH, Langridge S, Marrows CH. "Temperature controlled motion of an antiferromagnet-ferromagnet interface within a dopant-graded FeRh epilayer." APL Materials. 2015;3:041802. Available at: https:// doi.org/10.1063/1.4907282.

- [13] Uhlíř V, Arregi JA, Fullerton EE. "Colossal magnetic phase transition asymmetry in mesoscale FeRh stripes." Nature Communications. 2016;7:13113. Available at: https://doi. org/10.1038/ncomms13113.

- [14] Pressacco F, Sangalli D, Uhlíř V, Kutnyakhov D, Arregi JA, Agustsson SY, Brenner G, Redlin H, Heber M, Vasilyev D, Demsar J, Schönhense G, Gatti M, Marini A, Wurth W, Sirotti F. "Subpicosecond metamagnetic phase transition driven by non-equilibrium electron dynamics." 2021. Cornell University Library, available at: <a href="https://arxiv.org/abs/2102.09265">https://arxiv.org/abs/2102.09265</a>.

- [15] Yang JJ, Strukov DB, Stewart DR. "Memristive devices for computing." Nature Nanotechnology. 2013;8:13-24. Available at: https://doi.org/10.1038/nnano.2012.240.

- [16] Prezioso M, Merrikh-Bayat F, Hoskins BD, Adam GC, Likharev KK, Strukov DB. "Training and operation of an integrated neuromorphic network based on metal-oxide memristors." Nature. 2015;521:61-64. Available at: https://doi. org/10.1038/nature14441.

- [17] Moore GE. "Cramming more components onto integrated circuits." *Proceedings of the IEEE*. 1998;86(1):82–85. Available at: https://doi.org/10.1109/JPROC.1998.658762.

- [18] Feynman RP. "There's plenty of room at the bottom [data storage]." Journal of Microelectromechanical *Systems*. 1992;1(1):60–66. Available at: <a href="https://doi.">https://doi.</a> org/10.1109/84.128057.

- [19] Feynman R. "Infinitesimal machinery." Journal of *Microelectromechanical Systems.* 1993;2(1):4–14. Available at: https://doi.org/10.1109/84.232589.

# Optical Coprocessor Generates Bright Future for Probabilistic Computing

John T. Daly

[Photo credit: iStock.com/Михаил Руденко]

n 2006, a team of researchers published results for a new type of microprocessor architecture dubbed probabilistic complementary metal-oxide semiconductor (PCMOS) [1]. It used 30 times less power than conventional CMOS to perform computations. MIT Technology Review later recognized probabilistic computing as one of the 10 technologies "most likely to change the way we live" [2]. Probabilistic computers can solve complex problems by storing and processing states of zeros and ones that are indeterminate with some probability. They cannot always be guaranteed to provide the same solution to a given problem run more than once, but they can be built using hardware that runs extremely fast and at very low power. Spurred on by these early successes, the Defense Advanced Research Projects Agency (DARPA) Unconventional Processing of Signals for Intelligent Data Exploitation (UPSIDE) program began to explore applications of probabilistic computing to feature extraction from sensor imaging. Their image-processing pipeline used the physics of emerging probabilistic devices including analog nonvolatile memory. In the end, they demonstrated a 100-times performance increase and 1,000-times power efficiency improvement compared to traditional CMOS [3]. Considering these impressive results, why has probabilistic computing not changed the way we live like MIT Technology Review suggested? The answer to that question is multifaceted, much like the probabilistic devices themselves, but behind all the challenges in implementing probabilistic computing, there lies a common thread of nondeterminism.

Nondeterministic hardware is computer hardware that has the capacity to an incomputer hardware. that has the capacity to provide more than one answer for at least some, but not necessarily all, operations that have a single correct answer. In a word, it is unpredictable. Nondeterminism is the reason that every application of probabilistic computing to date has been highly specialized, both in terms of the problems it solves and the underlying technologies it uses to achieve nondeterminism. Only certain types of applications are amenable to unpredictability. The DARPA UPSIDE program achieved success with feature extraction from sensor imaging using a particular architecture and technology. What other technologies and applications stand to benefit from these types of physics-based approaches to computation? One such technology is optics. Optics is subject to thermodynamic noise by its basic physics, so it is reasonable to expect nondeterminism in an optical computing device. Optics is an inherently analog technology where both electron and photon noise contribute to the nondeterminism.

This article will explore the potential for using emerging nanophotonic devices to deliver optical arithmetic coprocessors for fast, energy-efficient computing. Such an approach exemplifies the high-performance computing (HPC) codesign methodology, whereby computer systems are purpose-built with specific application requirements in mind.

### The application: Multiplication

Most digital computers implement standard precision multiplication using a straightforward cross-product scheme where every digit of the multiplicand multiplies every digit of the multiplier. Such a scheme is said to be quadratic in its complexity, since the number of operations required to complete the muliplication is proportional to the square of the size of the numbers. For small numbers, with fewer than a few hundred bits, this is entirely adequate, but for larger numbers, there are a variety of "subquadratic" algorithms that trade off additional complexity for reduced asymptotic complexity. Of these approaches, Fourier multiplication is of particular interest because of its natural connection to optics [4].

### Fourier multiplication

By the convolution theorem, described in <u>figure 1</u>, we know we can write the Fourier transform of a

$$\mathcal{F}\{f\} = \int_{-\infty}^{\infty} f(x) \, e^{-ixt} \, dx$$

$$\mathcal{F}\{f * g\} = \mathcal{F}\{f\} \odot \mathcal{F}\{g\} \ \Rightarrow \ f * g = \mathcal{F}^{-1}\big\{\mathcal{F}\{f\} \odot \mathcal{F}\{g\}\big\}$$

**FIGURE 1.** The Fourier transform  $P\{f\}$  of a continuous function f(x) is defined above. The convolution theorem states that the Fourier transform of the convolution of two functions is equal to the pointwise product of their Fourier transforms. Since convolution in the discrete domain is equivalent to polynomial multiplication, this suggests a straightforward method of multiplying using a pointwise product and the forward and inverse Fourier transforms.

convolution as a pointwise product of Fourier transforms [5]. In other words, by Fourier transforming the multiplier and multiplicand of a product, we can reduce the complexity of the multiplication from quadratic (i.e.,  $O(n^2)$ ) to linear (i.e., O(n)), but at the cost of calculating the Fourier transforms of the inputs and inverse Fourier transforms of the output. Since the Fourier transform is  $O(n \log n)$ , a relatively expensive calculation on a digital computer, Fourier multiplication is typically limited in its application to very large numbers (e.g., thousands of digits).

In order to enable our optical coprocessor to scale to the very large numbers, it will need an efficient method of accumulating larger numbers of low-precision multiplications into a single high-precision multiplication. A residue number system (RNS) is one way to build a bridge between low-precision and high-precision arithmetic [6]. The residue number system enables calculation with arbitrarily large numbers by "breaking down" the numbers into sets of smaller numbers using properties of residue arithmetic as illustrated in <u>figure 2</u>. Given a multiplication problem with very large numbers, RNS allows us to break that problem down into a collection of smaller, independent operations which can be implemented in parallel. To utilize this approach however, our optical coprocessor will need to perform many, many calculations of  $(a \times b)$  mod m very efficiently for different values of *m* and all in parallel.

### Montgomery multiplication

In the previous section, we described at a high level the Fourier transform approach to multiplication and how we intended to apply it to very large numbers by implementing them as a collection of lower-precision

$$(a+b) \bmod m = ((a \bmod m) + (b \bmod m)) \bmod m$$

$$(a-b) \bmod m = ((a \bmod m) - (b \bmod m)) \bmod m$$

$$(a \times b) \bmod m = ((a \bmod m) \times (b \bmod m)) \bmod m$$

**FIGURE 2.** Residue number system (RNS) arithmetic makes use of a simple theorem of number theory that the remainder of a binary operation divided by m is equal to that same binary operation applied to the remainder of each of the operands. This holds true for the binary operators addition, subtraction, and multiplication.

modular multiplications all operating in parallel. In this section, we will look in more detail at the mathematics of combining Fourier multiplication and modular multiplication in the same optical coprocessor without using division, which would be extremely difficult to implement in optics. The solution is to reformulate the modular multiplication problem using Montgomery multiplication [7]. Montgomery recognized that it was often most efficient to rewrite the modular multiplication problem in a different "domain" where performing the division is much, much easier, as illustrated in figure 3.

With the Montgomery multiplication, we have all the necessary mathematical machinery to describe the operation of our optical coprocessor for easy and efficient multiplication of very large numbers. In the next section, we will consider why and how this approach can be implemented using optics technology.

### The technology: Optical computing

Optical computing—performing calculations using photons instead of electrons—is an idea that has been around for decades [8, 9]. Like many competing non-CMOS technologies, it ultimately lost out to the exponential growth of transistor counts in CMOS. Optics, being fundamentally limited by the wavelength of light, cannot attain the density of transistors. Furthermore, as an analog technology that is typically limited in precision, optical computing does not compete with digital technologies in terms of computational accuracy. However, with the recent slowing of transistor scaling accompanied by advances in emerging nanophotonic devices, there is renewed interest in exploring the role of optics in computing.

The remainder of this section will describe a coprocessor design based on Fourier optics and discuss possibilities and challenges of improving that design with emerging nanophotonic technology.

### Macro-scale optics

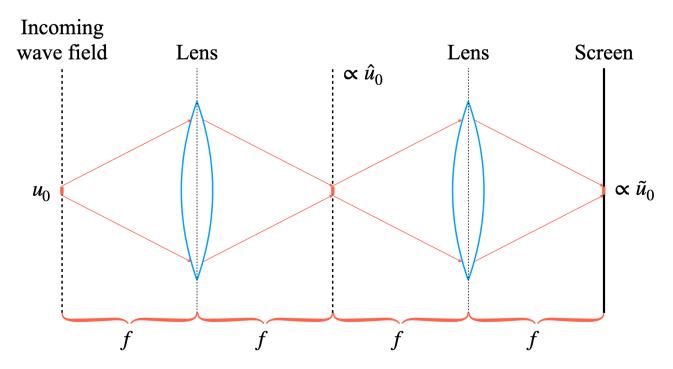

Fourier multiplication is known to be faster than traditional schoolbook multiplication, but it is typically not implemented in digital computing because of the time and energy overhead for performing the required Fourier transforms. However, optical computers can complete the Fourier transform with zero overhead using simple lenses and masks. An optically implemented Fourier transform can be used to simplify the multiplication of two *n*-digit numbers. To multiply with digital electronics, two *n*-digit numbers are represented as polynomials in powers of two. Digitally multiplying these to numbers has the same complexity as a convolution (i.e.,  $O(n^2)$ ). If we use  $F\{f\}$  however, we can convert this convolution in the time domain to pointwise multiplications in the frequency domain (complexity O(n)). The long-range interference of coherent photons enables "on-the-fly" Fourier transform computation using lenses and masks. Figure 4 illustrates a standard four focal-lengths long (4-f) optical system [10] using the symmetric property of the transform and depicting lines as exemplar rays. The optical domain produces an O(1) Fourier transform compared to digital electronics where the transform is a costly  $O(n \log n)$ .

Given

$$c = (a \cdot b) \mod m$$

choose  $r = 2^k > m$

$$\bar{x} = x \cdot r \mod m \text{ and } M = -m^{-1} \mod r$$

$$\downarrow \downarrow$$

$$\bar{c} = \frac{\bar{a} \cdot \bar{b} + m \cdot \left( \left( \bar{a} \cdot \bar{b} \cdot M \right) \mod r \right)}{r}$$

**FIGURE 3.** Montgomery multiplication provides a means to compute a modular multiplication problem without performing division by the modulus. Assuming that m is always odd, choosing an r>m that is a power of two allows us to replace division with simple bit shifting and masking in binary arithmetic. By precomputing M for a fixed set of moduli corresponding to the bases of our residue number system (see the previous section), Montgomery multiplication can be implemented very efficiently.

**FIGURE 4.** Figure representing a simple 4-f optical system. The wave field at the plane  $\hat{u}_0$  located one focal length behind the first lens is the exact Fourier transform of the input wave field at plane  $u_0$  By replicating this system with a second lens that performs the inverse transform, the wave field  $\tilde{u}_0$  will be a mirror image of  $\hat{u}_0$ . This is the building block of the optical modular multiplication coprocessor.

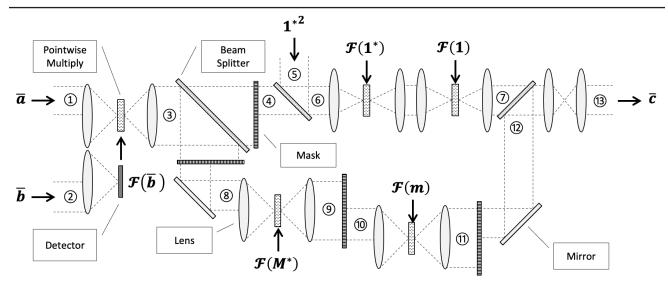

While division is generally difficult in optics, division by a power of two is easily done by masking off low-order bits. An implementation of Montgomery modular multiplication, described in the previous section of this article, is a natural approach in optics. Accommodating arbitrarily large inputs requires an efficient architecture that benefits from smaller, fixedsize multipliers. The Fourier transform in the optical domain uses a static configuration of source planes, lenses, and a fixed location objective image plane. One such system designed and evaluated both in simulation and on an optical bench is illustrated in figure <u>5</u>. The device performs the complete Montgomery multiplication in the Montgomery domain starting with two input values (step (1) and (2)) on the left, encoded as wave fields. The values are Fourier transformed and multiplied using a spatial light modulator (SLM) or equivalent device to impose spatially varying modulation to the light beam in the Fourier transform plane. This is how we accomplish the pointwise multiplication of the light intensity. Following the multiply of  $\bar{a} \times \bar{b}$  (step (3)), the result is divided into two

paths by a beam splitter. The bottom path computes the  $m((\bar{a} \times \bar{b} \times M) \mod r)$  term of the Montgomery multiplication using a sequence of fixed masks and filters (steps (8) through (12)), while the top path applies phase corrections to  $\bar{a} \times \bar{b}$  in order to correctly "add" it to the result of the bottom path (steps (4) through (7)). The result is masked to achieve the final division by *r* required to recover the solution  $\bar{c}$  (step (13)).

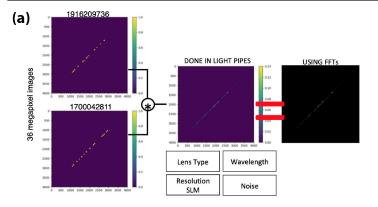

Figure 6 demonstrates a technique to encode 16-bit unsigned integers into the wave field. Numerical values are represented by the intensity of points of light along a diagonal. Lighted points correspond to binary one and dark spaces correspond to zero. The layout avoids optical smearing and "cross-talk" between pixels in the two-dimensional Fourier transform since no pixel is horizontally or vertically aligned with any other pixel. After a "multiplication," the light intensities represents a range of values from dark to light that encode the result. Discrete convolution differs from multiplication in that it does not perform carries between digits. The entire contribution of each pointwise

**FIGURE 5.** In this design of a macro-scale optical device for modular multiplication  $(a \times b) \mod m$  using the technique of Montgomery described in the previous section, values of  $\bar{a}$ ,  $\bar{b}$ , and M are assumed to be precomputed. Asterisks indicate locations where the image plane is reversed (i.e., mirror image).

input digit multiplication is encoded in each output digit. The multiplier was evaluated with the help of collaborators at George Washington University using both the LightPipes simulator [11] and an optical bench prototype illustrated in figure 6. Simulation and prototype agreed with the theory to 16 bits of precision, thus providing an initial validation of the all-optical approach to multiplication. The prototype anecdotally verified the probabilistic nature of the device as well, since initial results were correct "only about" 80 percent of the time.

Despite the advantages of using an all optical system for multiplication, the bulkiness of macro-scale optical components, in particular the lenses, makes such a system too large (i.e., linear dimensions on the order of 10–100 centimeters) to be practical. Further, the performance of the macro-scale system is limited to the sub-megahertz regime by the speed of the SLM. In terms of energy efficiency, we are able to make an initial estimate based on our simulation results. Assuming that one photon per detector site is sufficient for room temperature detection [12], the end-to-end photon loss across the entire modular multiplication device in figure 5 is around 3,000 times. With a photon energy of approximately 10<sup>-18</sup> Joules for 200-nanometer light, the projected efficiency of the device is about 1 nanojoule per operation for a 16-bit

modular multiply. This is not particularly competitive compared to modern application-specific integrated circuit (ASIC) designs, where the same calculation implemented in 16-nanometer CMOS technology would consume closer to 10 picojoules [13]. Given the limitations of macro-scale optics, in the next section we will turn our attention to consideration of emerging nanoscale optical devices.

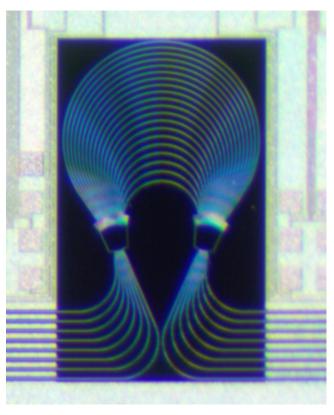

### Promise and challenge of nanoscale optics

Nanophotonics using metamaterials enables the design and engineering of novel optical systems, overcoming the limitations of macroscale optics. Metamaterials are heterogeneous or highly structured nano-engineered media for next-generation optical systems. These are materials with electromagnetic responses that cannot be obtained from conventional media. For instance, surface plasmon polaritons (SPP) have a square-root dispersion enabling "very high k-vectors for a finite frequency." In other words, energy can be confined within the metamaterial with very little dispersion. These materials operate with sub-wavelength, nano-engineered heterostructures that allow customization of optical properties. Using metalenses and reconfigurable metasurfaces, a 4-f optical system can be constructed in tens of micrometers [14]. Where a macro-scale optical system's

performance is limited by the configuration speed of the SLM to sub-megahertz performance, the small electrical capacitance of a nanoscale reconfigurable metasurface allows for processing at rates above the gigahertz range [15]. We can bound the required power by considering the minimum detectability at the photodetector, a value typically about tens of nanowatts for high-speed detectors. Assuming visible or near-infrared optical frequencies, and a bandwidth of tens of gighertz, we find a minimum optical power required for the intermediate result of a 16-bit modular multiply to be 6.5 microwatts. A 10-gigahertz system running at 6.5 microwatts yields a computational efficiency of around 1 femtojoule per 16-bit modular multiply. That is four orders of magnitude more energy efficient than the 10 picojoules per multiplication based on digital CMOS technology. Nanophotonics has potential to be a game changer for high-speed, energy-efficient computation.

The promise of nanophotonics is not without challenges though. Several of the most significant technical challenges are summarized below. They will need to be solved before devices like the one described in this article can fully be realized.

Attenuation through the optical system—

Several stages of the subsystem provide less than half the energy to the subsequent stage. Using a phase synchronous light source makes the noise less than it might be, but where the signal is at low levels, nonlinearities, path length differences,

- and shot noise cause additional loss in the signal-to-noise ratio.

- ▶ Electrical-optical and optical-electrical conversions—Moving data from electrical to optical domains expends energy as much as 10¹² above the optical calculation energy. This means that chaining multiple operations in the optical domain will be critical, and accumulated inaccuracies need to be managed.

- As with most emerging technologies, there are a variety of engineering challenges to be overcome in order to manufacture meta-devices at acceptable cost and yield. Feature variation will be a concern in a production-scale computing system and will need to be addressed as the technology continues to mature.

### Conclusion

Emerging nanophotonic technology offers an enticing opportunity for multiple orders of magnitude improvement in arithmetic processing efficiency similar to the gains demonstrated by DARPA UPSIDE for image feature extraction. The potential of computing in excess of a billion operations per second while expending femtojoules per operation could provide significant performance advantages beyond the capabilities of digital CMOS. The future looks very bright for probabilistic computing based on optical coprocessors.

**FIGURE 6.** (a) Here is the result of a LightPipes simulation compared to an exact fast Fourier transform (FFT) calculation and (b) a physical test on an optical workbench. Experiments performed by George Washington University (GWU) validated a multiplier subcomponent using a spatial light modulator (SLM) and comparing the result to those calculated based on theory using FFTs. The results shows a bit-for-bit exact match from theory to simulation to experiment. [Photo credit: The SORGER Group at George Washington University (GWU).]

### References

- [1] Chakrapani LN, Akgul BES, Cheemalavagu S, Korkmaz P, Palem KV, Seshasayee B. "Ultra efficient embedded SOC architectures base on probabilistic CMOS (PCMOS) technology." In: *Proceedings of the Design Automation and Test in Europe Conference (DATE)*; 2006: pp. 1–6. doi: 10.1109/DATE.2006.243978.

- [2] Jonietz E. "Probabilistic chips." *MIT Technology Review.* 2008 Feb 18. Available at: <a href="https://www.technologyreview.com/technology/tr10-probabilistic-chips/">https://www.technology/tr10-probabilistic-chips/</a>.

- [3] Hammerstrom D. "UPSIDE/cortical processor study: DISTAR approved," presented at the *IEEE Rebooting Computing Summit IV*; 2015 Dec 7; Washington, DC. Available at: <a href="http://rebootingcomputing.ieee.org/images/files/pdf/RCS4HammerstromThu515.pdf">http://rebootingcomputing.ieee.org/images/files/pdf/RCS4HammerstromThu515.pdf</a>.

- [4] Timmel AN, Daly JT. "Multiplication with Fourier optics simulating 16-bit modular multiplication." In: *Proceedings of 2018 IEEE International Conference on Rebooting Computing (ICRC)*; 2018 Nov 7; McLean, VA: pp. 1–11. Available at: <a href="http://doi.org/10.1109/ICRC.2018.8638618">http://doi.org/10.1109/ICRC.2018.8638618</a>.

- [5] Schönhage A, Strassen V. "Schnelle multiplikation großer zahlen." *Computing.* 1971;7:281–292. doi: 10.1007/DF02242355.

- [6] Bajard JD, Eynard J, Merkiche N. "Montgomery reduction within the context of residue number system arithmetic." *Journal of Cryptographic Engineering.* 2018;8(3):189–200. Available at: <a href="http://doi.org/10.1007/s13389-017-0154-9">http://doi.org/10.1007/s13389-017-0154-9</a>.

- [7] Montgomery PL. "Modular multiplication without trial division." *Mathematics of Computation*. 1985; 44(170):519–521. Available at: <a href="http://doi.org/10.1090/50025-5718-1985-0777282-X">http://doi.org/10.1090/50025-5718-1985-0777282-X</a>.

- [8] Sawchuk AA, Strand TC. "Digital optical computing." *Proceedings of the IEEE.* 1984;72(7). doi: 10.1109/PROC.1984.12937.

- [9] Feitelson DG. Optical Computing: A Survey for Computer Scientists. Cambridge (MA): MIT Press; 1988. ISBN: 978-0-262-56062-7.

- [10] Candes E. MATH 262/CME 372: Applied Fourier Analysis and Elements of Modern Signal Processing. Lecture 17. 2021 Mar 11. Available at: <a href="https://statweb.stanford.edu/~candes/teaching/math262/Lectures/Lecture17.pdf">https://statweb.stanford.edu/~candes/teaching/math262/Lectures/Lecture17.pdf</a>.

- [11] Jiale J, Minhao Z, Gupta P, Shengqi Y, Rubin SM, Garret G, Jin H. "A CAD tool for design and analysis of CNFET circuits." In: *Proceedings of 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC)*; 2010 Dec 15–17: pp. 1–4. Available at: <a href="http://doi.org/10.1109/EDSSC.2010.5713735">http://doi.org/10.1109/EDSSC.2010.5713735</a>.

- [12] Ma J, Masoodian S, Starkey D, Fossum E. "Photon-number-resolving megapixel image sensor at room temperature without avalanche gain." *Optica*. 2017;4(12). doi: 10.1364/OPTICA.4.001474.

- [13] Pohokar SP, Sisal RS, Gaikwad KM, Patil MM, Borse R. "Design and implementation of 16x16 multiplier using Vedic mathematics." In: *International Conference on Industrial Instrumentation and Control (ICIC)*; 2015 May 28–30: pp. 1174–1177. doi: 10.5120/15802-4641.

- [14] Khorasaninejad M, Chen WT, Devlin RC, Oh J, Zhu AY, Capasso F. "Metalenses at visible wavelengths: Diffraction-limited focusing and subwavelength resolution imaging." *Science.* 2016;352:1190–1194. Available at: <a href="http://doi.org/10.1126/science.aaf6644">http://doi.org/10.1126/science.aaf6644</a>.

- [15] Yao Y, Shankar R, Kats MA, Song Y, Kong J, Loncar M, Capasso F. "Electrically tunable metasurface perfect absorbers for utrathin mid-infrared optical modulators." *Nano Letters*. 2014;14(11):6526–6532. doi: 10.1021/nl503104n.

Lauren Huckaba

igh-performance computing (HPC) systems are growing increasingly complex. With this, the error rate of computation is growing and faults are becoming harder to diagnose and correct. Traditionally, the field of resilience is dedicated to developing methods to keep applications running to a correct solution in spite of errors, but the more complex the computer, the more costly these methods become. Rather than expend energy combating these faults, one possibility is to accept these errors and allow nondeterminism in our computations in exchange for greater energy efficiency.

Further, computer applications must process volumes of data so large that the energy and performance costs of moving this data from memory to the central processing unit (CPU) dominates the total cost of computation. Processing in memory (PIM) is a novel, non-von Neumann model of computation that saves energy by doing computation and storing data in the same place [1].

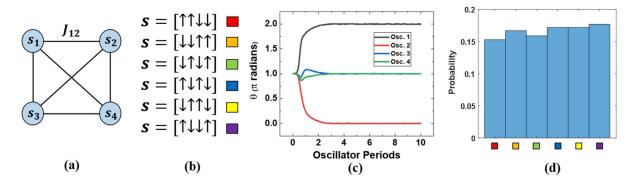

In this article, we describe a probabilistic PIM computer, made entirely of existing electronic components, based on the Ising model. We discuss how we can use an Ising model in inverse ways to solve two types of important problems.

### The Ising model and the Ising problem

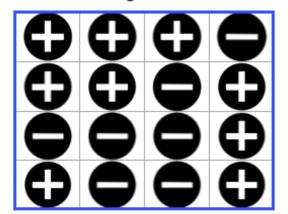

An Ising model is a mathematical model originally formulated to describe ferromagnetism in statistical mechanics. It consists of a lattice of spins in one of two states (see <u>figure 1</u>).

There is a measure of the surrounding magnetic field corresponding to each spin and a measure that denotes the interaction between each pair of spins. We call these measurements "weights." We can write down an expression for the total energy of the system in terms of the spin states and weights. The expression for total energy is known as the Hamiltonian (see figure 2).

In the physical world, an Ising system has the important property that once configured with a set of weights, the spins try to settle to a configuration that yields the lowest total energy. It achieves this state with some probability and this is where the nondeterminism comes in.

The goal of the Ising Problem is to fix a set of weights and find the configuration of spins that minimizes the Hamiltonian. The Ising Problem is a combinatorial optimization problem in which the set of local minima grows exponentially as a function of the number of spins, making it NP-hard. Many other combinatorial optimization problems, such as the traveling salesman problem and the MAX-CUT problem, can be mapped to the Ising model. Hence, the ability to efficiently solve the Ising Problem can

### Ising Model

**FIGURE 1.** An Ising model is a lattice of spins, some positive, or taking the value 1, and some negative, or taking the value -1.

$$H(s) = \sum_{i=1}^{n} h_i s_i + \sum_{i,j=1}^{n} J_{ij} s_i s_j$$

**FIGURE 2.** In the equation above, H(s) represents the Hamiltonian or total energy of the Ising system when in configuration s. Here,  $s = (s_1,...,s_n)$  is the configuration of spins,  $h_i$  is the measure of the magnetic field surrounding spin  $s_i$ , and  $J_{ij}$  is the measure of the interaction between  $s_i$  and  $s_j$ . We refer to the  $h_i$ 's and  $J_{ij}$ 's as "weights" in this article.

potentially lead to solutions to a large class of other combinatorial optimization problems [2].

# Using an Ising model to perform arithmetic—the inverse Ising problem

The Ising problem above consists of fixing weights and determining the appropriate configuration of spins. Alternately, we can solve the inverse Ising problem by fixing a configuration of spins and finding the weights that minimize the Hamiltonian. In doing this, we can use an Ising model to do arithmetic.

We can fix a set of spins that corresponds to a correct arithmetic equation. Then we solve an optimization problem where we determine the weights that minimize the Hamiltonian. We also add constraint inequalities to our optimization problem to ensure that configurations corresponding to incorrect answers do not give a lower total energy. Even for small problems, say 3-bit multiplication, the number of constraint inequalities is quite large. For this reason, we do not give a concrete example in this article.

The weights found by solving the optimization problem can be used to tune an Ising machine or simulator built to solve the Ising problem. As described in the previous section, the machine will then try to settle to a configuration that gives the lowest total energy. In this case, that configuration is the one that corresponds to the correct answer to our multiplication problem. Because of the way we set our constraints above, getting a correct answer is more likely than getting an incorrect answer. In the following subsection, we model this process mathematically.

At first glance, it may seem as though the inverse Ising problem is easier to solve than the Ising problem

since Hamiltonian is clearly quadratic in the spin variables, but linear in the *h*'s and *J*'s. However, after setting up even a small inverse Ising problem, it becomes clear that the number of constraint equations grows exponentially in the number of spins. As such, it quickly becomes difficult to multiply numbers of more than a just a few bits in this way, and alas, the inverse Ising problem is NP-hard as well.

The Resilience and Probabilistic Computing team at the Laboratory for Physical Sciences (LPS) has spent the last few years working on the inverse Ising problem. We have a solution technique that involves an internally developed two-stage algorithm that first searches for a set of feasible parameters and then solves a system of constraints derived from the feasible parameters. Both stages have exponential complexity, but our team improved the solution time of a 3-bit multiplier from 120 days to under 10 minutes for a system of 32,000 constraints by reducing the problem to polynomial complexity. We also successfully solved the system of 267,000,000 constraints for the 4-bit multiplier. The total solve time was 27 days and used 5.5 terabytes of shared memory.

### A mathematics illustration

In the absence of an actual Ising machine, we can compute a probability. The probability that the system settles to a certain configuration for a given set of weights is called the Boltzmann probability. It depends on the total energy of the system when in this configuration, as well as the noise present in the system (see figure 3).

Figure 4 (on the following page) shows probabilities of solutions to 2-bit multiplication problems. After solving the inverse Ising problem, we calculated the Boltzmann probability for each configuration, both those corresponding to incorrect solutions and the configuration corresponding to the correct solution, and added some noise into our computation. This illustrates the results of simulating the nondeterminism present in an actual Ising machine. Properly setting our constraints described above gives us control over our nondeterministic computation so that there is hope of obtaining a correct answer. In this model, there is no need for error correction, which allows for a more energy-efficient computation than in a traditional digital machine.

$$\mathbf{Prob}_{\beta}(s) = \frac{e^{-\beta H(s)}}{\sum_{\sigma} e^{-\beta H(\sigma)}}$$

**FIGURE 3.** The equation above represents the probability that an Ising system settles to a configuration s.  $\beta$  represents the noise present. More specifically,  $\beta = 1/(k_B.T)$ , where T is the temperature of the system in kelvin and  $k_B$  is the Boltzmann constant. For the purpose of this article, we can think of  $\beta$  as simply the "noise term."

### **Hardware**

While the Ising model dates back to the 1920s, it was re-popularized much later by D-Wave Systems in an attempt to simulate quantum mechanical phenomena to speed up computation, including computation to solve the aforementioned combinatorial optimization problems. Recently, alternative classical methods to solve the Ising problem have emerged using optoelectronic parametric oscillators, memristor cross-bar arrays, electronic oscillators, and GPU-based algorithms [2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12].

An analysis of an optoelectronic coupled oscillator system revealed the potential for a significant speedup over digital computing algorithms when the number of oscillators (nodes) is large enough  $[\underline{13}]$ . Scaling up the optoelectronic oscillator Ising machine, however, remains challenging due in part to its high complexity and costly setup  $[\underline{5}, \underline{6}, \underline{13}]$ .

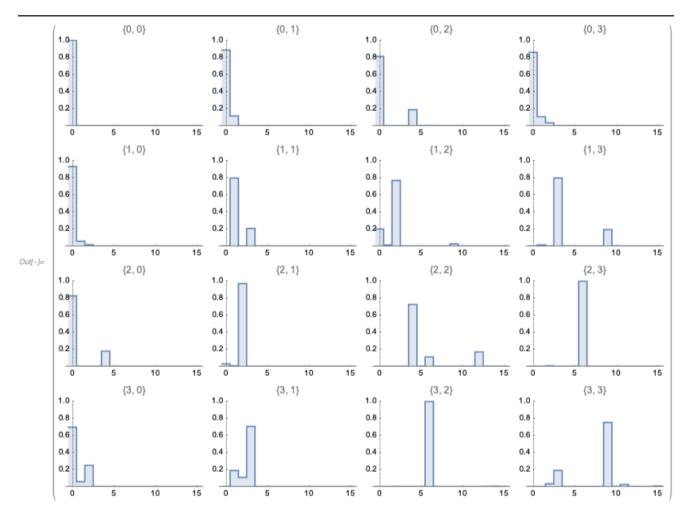

However, an all-electronic oscillator concept initially proposed by Wang and Roychowdhury introduces the idea of creating a similar system using readily available electronic components interconnected in a parallel fashion and is particularly well suited for chip-scale integration and scaling using present day technologies [2, 9].

Sync Computing and MIT Lincoln Laboratory (MIT-LL) built on this initial work and demonstrated a 4-node, fully-connected, differential LC (inductor-capacitor) oscillator-based analog circuit with standard electronic components which accurately maps to the Ising model. To the best of our knowledge, this is the first demonstration of an all-electronic oscillator-based Ising machine with multi-bit weights [2]. In [2], Chou et. al detail a statistical analysis that provides insight into the viability of these systems as computing platforms when scaled to larger node

**FIGURE 4.** This illustrates the nondeterminism inherent in an Ising machine. The horizontal axis is possible answers and the vertical axis is the probability of a getting a certain answer. These are plots of the probabilities of getting different solutions to 2-bit multiplication problems. For example, the upper right corner represents  $0 \times 3$  as denoted by the heading  $\{0,3\}$ . We see here that we get the answer 0 most of the time, but that the answer is wrong sometimes. If we were to increase the noise term,  $\beta$ , for this calculation, we would get a wrong answer even more often.

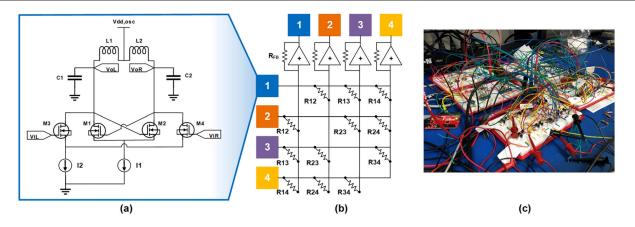

counts. <u>Figure 5</u> shows a circuit diagram of the LC oscillator circuit that employs a differential injection-locked frequency divider, the oscillators arranged in a cross-bar array, and the full breadboard system [2, 15]. Currently, Sync Computing is building a 16-node system. <u>Figure 6</u> shows a photo of the printed circuit board.

### Simulation—coupled oscillator system

A well-known benchmark optimization problem is the MAX-CUT problem from graph theory. Following an example in [2], we discuss a small MAX-CUT problem below using a simulation by MIT-LL of the coupled oscillator system.

Given an undirected graph, the MAX-CUT problem consists of finding a partition of that graph into two sets so that the number of edges between the two sets is as large as it can be. It has been shown previously that these graphs can be represented by a network of coupled nonlinear oscillators whose phase dynamics are described by the Kuramoto model, and that this model maps directly to the Ising Hamiltonian if the phases of these oscillators take values of either 0 or 180 degrees. As such, the Kuramoto model is the basis for the MIT-LL simulation [2, 9, 14].

An example of a 4-node (4-spin) system is shown in figure 7a (on page 24). This can also be thought of as a graph with four vertices such that every vertex is

FIGURE 5. (a) This circuit diagram depicts the LC (inductor-capacitor) oscillator circuit. (b) In this diagram, the oscillators are arranged in a cross-bar array. (c) This photo shows the full breadboard system [2]. [Photo credit: MIT Lincoln Laboratory.]

connected to every other vertex. If we let J = 1 for all connections and h = 0, then the Ising problem, in this case, has six solutions shown in figure 7b. One of these solutions is shown in terms of phase in figure 7c. Here, the four spins were intentionally configured to an incorrect solution state and they settled at one of the six correct solution states as expected. Additionally, the system settles to the ground state within three oscillation cycles in this example. Figure 7d shows the results of running the simulation 1,000 times with random initial configurations. We see that the system settles to a correct solution state fairly uniformly [2].

### The simulator and the inverse Ising problem

We (i.e., the LPS Resilience and Probabilistic Computing team) used the MIT-LL simulator to validate the results we obtained from solving the inverse Ising problem. We obtained weights from solving the inverse Ising problem, and we used those weights to tune the simulator. The results of using the simulator look similar to figure 4 where we computed Boltzmann probabilities and plotted the results. We found that using the simulator to validate the weights

FIGURE 6. Photo of the printed circuit board of the 16-node system. [Photo credit: Sync Computing.]

**FIGURE 7.** (a) This diagram depicts a fully connected 4-node system, for which (b) is the solution set where an up arrow is a positive spin and a down arrow is a negative spin. The graph in (c) shows the first solution in terms of phases, and (d) is a histogram of the results of running the simulation 1,000 times [2]. [Photo credit: MIT Lincoln Laboratory.]

was a step up from computing the Boltzmann probabilities. Our next step is to validate our results using hardware in place of the simulation.

### Looking ahead

While quantum computers, like D-Wave, have the potential to solve these NP-hard combinatorial optimization problems, scaling up the number of quantum bits in these systems remains a great challenge. On the other hand, it is possible to build a probabilistic computer out of standard electronic components, as demonstrated by Sync Computing [2]. This allows for faster and more cost-effective scaling. It is reasonable to believe that this all-electronic Ising machine is scalable from four nodes to hundreds of nodes within just a few years. A limiting factor of such a machine is indeed physical space. For the more we scale up, the more oscillator circuits we must add. This does suggest that in order to build an Ising machine for practical use, we will want to explore additional technologies. However, an Ising machine with hundreds of nodes is enough to validate nontrivial results we obtain mathematically that are too large to validate in simulation. While thousands of nodes are necessary for practical use, this system is a step in the right direction and shows promise for a future that includes probabilistic computers.

### References