# National Security Agency Cybersecurity Technical Report

# DoD Microelectronics: Field Programmable Gate Array Level of Assurance 1 Best Practices

May 2024

U/OO/156781-24 PP-24-1960 Version 1.1

This document was created through collaboration with each of the JFAC labs: National Security Agency (NSA), Air Force Research Lab (AFRL) RYDT, Naval Surface Warfare Center (NSWC) Crane, and Army Development Command (DEVCOM)/AVMC.

For additional information, guidance, or assistance with this document, please contact the Joint Federated Assurance Center (JFAC) at <a href="mailto:JFAC\_HWA@radium.ncsc.mil">JFAC\_HWA@radium.ncsc.mil</a>.

## **Notices and history**

#### Document change history

| Date          | Version | Description              |

|---------------|---------|--------------------------|

| December 2022 | 1.0     | Initial Publication      |

| May 2024      | 1.1     | Minor updates throughout |

#### Disclaimer of warranties and endorsement

The information and opinions contained in this document are provided "as is" and without any warranties or guarantees. Reference herein to any specific commercial products, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement, recommendation, or favoring by the United States Government, and this guidance shall not be used for advertising or product endorsement purposes.

## **Publication information**

#### Author(s)

National Security Agency Cybersecurity Directorate Joint Federated Assurance Center

#### **Contact information**

Joint Federated Assurance Center: <u>JFAC\_HWA@radium.ncsc.mil</u> General Cybersecurity Report Inquiries: CybersecurityReports@nsa.gov

Defense Industrial Base Inquiries and Cybersecurity Services: <u>DIB\_Defense@cyber.nsa.gov</u> Media inquiries / Press Desk: Media Relations, 443-634-0721, MediaRelations@nsa.gov

# **Purpose**

This document was developed in furtherance of NSA's cybersecurity missions. This includes its responsibilities to identify and disseminate threats to National Security Systems and Department of Defense information systems, and to develop and issue cybersecurity specifications and mitigations. This information may be shared broadly to reach all appropriate stakeholders.

# **Executive summary**

In support of securing Field Programmable Gate Array (FPGA) based systems from adversary influence during the manufacturing process, this report outlines the categories of relevant threats and the best practices for mitigating them at Level of Assurance 1 (LoA1). LoA1 captures the threats most likely to be exercised against a DoD system based upon their low cost and high value of return. At this level, these threats have the following characteristics:

- Access Exploit a single available point of access,

- **Technology** Use existing public technology,

- Investment Require minimal investment of resources,

- Value of effect Disable or subvert system capabilities, and

- **Targetability** Are inherently targetable and controllable.

Organized by threat, this report provides multiple technical mitigations to choose from to mitigate each threat and allow the program the best fit for their program needs. The following table identifies the threat descriptions (TD) addressed by this guidance.

| #      | Threat description (TD)                                           |

|--------|-------------------------------------------------------------------|

| TD 1   | Adversary utilizes a known FPGA platform vulnerability            |

| TD 2   | Adversary inserts malicious counterfeit                           |

| TD 3   | Adversary compromises application design cycle                    |

| TD 4   | Adversary compromises system assembly, keying, or provisioning    |

| TD 5   | Adversary compromises third-party soft intellectual property (IP) |

| TD 6   | Adversary swaps configuration file on target                      |

| TD 7   | Adversary substitutes modified FPGA software design suite         |

| TD 8 * | Adversary modifies FPGA platform family at design                 |

| TD 9   | Adversary compromises single-board computing system (SBCS)        |

<sup>\*</sup> TD 8 is not a threat at LoA1; however, JFAC requests that DoD programs even at LoA1 provide information about FPGA device use as described in JFAC Survey Request. This information relates to TD 8 mitigations.

Each subsection in this report contains mitigations described in detail to enable clear implementation guidelines for DoD systems. Secondary documents are referenced in cases where the suggested mitigation is highly detailed, specific to individual FPGA platforms, or subject to frequent change. Appendix E: Checklists and data/documentation requirements contains a quick reference list of threats and associated data requirements.

Once the DoD program has mitigated these threats, they have achieved an assurance level of LoA1.

#### **Contents**

| DoD Microelectronics: Field Programmable Gate Array Level of Assu<br>Best Practices |          |

|-------------------------------------------------------------------------------------|----------|

| Executive summary                                                                   |          |

| •                                                                                   |          |

| Contents                                                                            |          |

| 1. Introduction                                                                     |          |

| 2. Terms                                                                            |          |

| 3. Overview of Level of Assurance 1 threats and mitigations                         |          |

| Complementary standards and guidance      Exclusions                                |          |

| 3.3 Document use                                                                    |          |

| 3.4 General Comments on Mitigations                                                 |          |

| 4. Threat Descriptions (TD)                                                         |          |

| TD 1: Adversary utilizes a known FPGA platform vulnerability                        | 8        |

| TD 1 mitigations                                                                    | 9        |

| TD 1 mitigation descriptions                                                        |          |

| Use caution when selecting tools or platforms                                       |          |

| Research vulnerabilitiesUse a revision control/version management system            |          |

| Enforce auditability                                                                |          |

| Perform a vulnerability data review                                                 |          |

| Perform routine employment monitoring                                               |          |

| Prevent a compromised insider                                                       | 12       |

| TD 2: Adversary inserts malicious counterfeit                                       | 12       |

| TD 2 mitigations                                                                    | 14       |

| TD 2 mitigation descriptions                                                        |          |

| Purchase from DoD authorized vendors and distributors                               |          |

| Follow storage and shipping guidanceValidate the authenticity of the FPGA device    |          |

| TD 3: Adversary compromises application design cycle                                |          |

| TD 3 mitigations                                                                    |          |

| Use cleared personnel in a cleared environment                                      |          |

| TD 3 mitigation descriptions                                                        |          |

| Track critical data in a revision control system                                    |          |

| Enforce auditability                                                                | 21       |

| Use a revision control/version management system                                    |          |

| TD 3.1: Mitigating the introduction of a compromised design into the application    | 22       |

| Isolate and store the application design                                            |          |

| Perform a reproducible build                                                        |          |

| TD 3.2: Mitigating the modification of test benches or plans to reduce coverage or  | •        |

| code  Execute a documented test plan                                                |          |

| Validate and verify test processes                                                  | 27<br>25 |

| Ensure the test environment is maintained via configuration management                                      | 25     |

|-------------------------------------------------------------------------------------------------------------|--------|

| Use a revision control/version management system                                                            | 25     |

| TD 3.3: Mitigating the introduction of a Trojan into the application design during development              | 26     |

| Ensure all design artifacts have a direct bi-directional link to approved requirements  Enforce peer review | 26     |

| Execute a documented test plan                                                                              |        |

| Implement, validate, and verify test processes                                                              | 28     |

| Select a formal "proof" process                                                                             | 28     |

| TD 3.4: Mitigating the introduction of compromised tooling or software into the environm                    | ent.29 |

| Accept only digitally signed software deliveries                                                            | 29     |

| Validate cryptographic hashes                                                                               |        |

| Research vulnerabilities                                                                                    |        |

| Use a revision control/version management system                                                            |        |

| Utilize a reproducible build process                                                                        |        |

| Select a formal "proof" process                                                                             |        |

| TD 3.5: Mitigating intrusion into the internal network                                                      |        |

| Use a revision control/version management system                                                            |        |

| Assign privileges and accesses based on roles                                                               |        |

| Control and monitor access                                                                                  |        |

| Research vulnerabilities  Purchase from DoD authorized vendors and distributors                             |        |

| Use protected computing environments                                                                        |        |

|                                                                                                             |        |

| TD 3.6: Mitigating risk from a compromised hire or employee  Enforce auditability                           |        |

| Track critical data in revision control                                                                     |        |

| Adopt a structured application design process                                                               |        |

| Review critical activities                                                                                  | 37     |

| Enforce reviewer criteria                                                                                   |        |

| TD 4: Adversary compromises system assembly, keying, or provisioning                                        |        |

| TD 4 mitigations                                                                                            |        |

| TD 4 mitigation descriptions                                                                                |        |

| Purchase from DoD and vendor authorized distributors                                                        |        |

| Follow storage and shipping guidance  Provide keys and configuration data                                   |        |

| Clear memory devices                                                                                        |        |

| Provision private keys                                                                                      |        |

| Protect the FPGA from attack during assembly and provisioning                                               |        |

| Authenticate the FPGA device                                                                                |        |

| TD 5: Adversary compromises third-party soft IP                                                             |        |

| TD 5 mitigations                                                                                            | 44     |

| TD 5 mitigation descriptions                                                                                |        |

| Purchase from DoD authorized vendors and distributors                                                       |        |

| Only accept IP that is unobfuscated                                                                         |        |

| Validate the cryptographic hash of the IP                                                                   |        |

| Check IP into revision control                                                                              | 45     |

| Examine IP for malicious functions                                         | 45 |

|----------------------------------------------------------------------------|----|

| TD 6: Adversary swaps configuration file on target                         | 45 |

| TD 6 mitigations                                                           | 47 |

| TD 6 mitigation descriptions                                               |    |

| Incorporate cryptographic authentication                                   |    |

| Authenticate configuration data each time the data is loaded               |    |

| Prevent direct read back                                                   |    |

| Use a CNSS/NIST-approved algorithm and key length                          |    |

| Disable operation or use of test access pins                               |    |

| Ensure authentication is enabled for application modifications             |    |

| TD 7: Adversary substitutes modified FPGA software design suite            |    |

|                                                                            |    |

| TD 7 mitigationsTD 7 mitigation descriptions                               |    |

| Purchase from DoD authorized vendors and distributors                      |    |

| Prevent automatic tool updates                                             |    |

| Use a protected computing environment                                      |    |

| Validate the cryptographic hash                                            |    |

| TD 9: Adversary compromises single-board computing system (SBCS)           |    |

| TD 9 mitigations                                                           |    |

| TD 9 mitigation descriptions                                               |    |

| Purchase from DoD authorized vendors and distributors                      |    |

| Authenticate the FPGA devices                                              | 55 |

| Populate and inspect the SBCS                                              | 55 |

| Document the steps taken to demonstrate compliance                         | 56 |

| 5. JFAC Survey Request                                                     | 56 |

| 6. Summary                                                                 | 57 |

| Appendix A: Standardized terminology                                       | 58 |

| Appendix B: IP reuse guidance                                              |    |

| Reuse Conditions                                                           | 61 |

| Reuse Scenarios                                                            |    |

| Appendix C: JFAC FPGA reporting template                                   |    |

| Appendix D: Guidance for embedded FPGA IP                                  | 68 |

| LoA1 Introduction                                                          | 68 |

| eFPGA Guidance                                                             |    |

| TD 3: Adversary compromises application design cycle                       | 68 |

| TD 4: Adversary compromises system assembly, keying, or provisioning       |    |

| TD 5: Adversary compromises third-party soft IP                            |    |

| TD 6: Adversary swaps configuration file on target                         |    |

| TD 7: Adversary substitutes modified FPGA software design suite            |    |

| TD 10: Adversary modifies FPGA software design suite                       |    |

| Appendix E: Checklists and data/documentation requirements                 |    |

| Checklist for TD 1: Adversary utilizes a known FPGA platform vulnerability |    |

| Checklist for TD 2: Adversary inserts malicious counterfeit                |    |

| Checklist for TD 3: Adversary compromises application design cycle         | 75 |

| Checklist for TD 4: Adversary compromises system assembly, keying, or provisioning | 86 |

|------------------------------------------------------------------------------------|----|

| Checklist for TD 5: Adversary compromises third-party soft IP                      | 88 |

| Checklist for TD 6: Adversary swaps configuration file on target                   | 89 |

| Checklist for TD 7: Adversary substitutes modified FPGA software design suite      | 90 |

| Checklist for TD 9: Adversary compromises single-board computing system (SBCS)     | 91 |

| Tables                                                                             |    |

| Table 1: LoA1 threats                                                              | 5  |

| Table 2: List of AS6171 slash sheets                                               | 18 |

### 1. Introduction

This document provides JFAC's recommended hardware assurance strategies for Field Programmable Gate Array (FPGA) devices used by DoD programs. The guidance outlined by this document provides hardware assurance to systems requiring Level of Assurance 1 (LoA1). Additionally, it provides the requisite strategies and details for implementing each threat mitigation. Secondary documents are referenced in cases where the suggested mitigation is highly detailed, specific to individual FPGA platforms, or subject to frequent change.

The mitigations included within this document are the responsibility of the program, to include all subcontractors. These mitigations are not written for third-party providers to use for the purpose of becoming "LoA" compliant. Since the third-party provider represents potential malicious access points and the program has no positive control over them, work or products coming from them should be verified against threats. Third-party statements of mitigation resolution are not satisfactory; the program has the responsibility to verify the mitigation. Third-party entities could include third-party IP providers (3PIP), software vendors, and manufacturers.

This guidance is meant to stand on its own and not require the participation of JFAC in the development process of a program's product, unless required by a specific mitigation. However, JFAC does remain at the ready to aid programs who seek to better understand this guidance, to incorporate a program specific mitigation, or are seeking alternatives to the guidance contained herein. For further information or support, please contact JFAC\_HWA@radium.ncsc.mil.

#### 2. Terms

To aid the reader, a glossary of terms is at the end of this document in <u>Appendix A</u>. However, it will be helpful to highlight several terms before proceeding. Below are several important terms to understand:

Application or application design – a DoD program's design that is programmed into an FPGA device. This can refer to the design in any of its various formats.

1

- Configuration file or data also known as a bitstream, this is the data used to configure the FPGA including the application design and all other programming information.

- FPGA device or device a specific individual FPGA packaged device.

- Hard IP a hardware design, also called intellectual property or IP, which is represented by its physical layout format. In FPGAs, this is IP that is embedded by the FPGA vendor into the FPGA physical design.

- Soft IP IP that is represented in a logical human readable format such as a hardware description language.

- Platform design the design of an FPGA family of devices, not just an individual device.

## 3. Overview of Level of Assurance 1 threats and mitigations

LoA1 requires mitigations against FPGA assurance threats that have the following characteristics:

- Access A single point of access to some portion of the FPGA supply chain.

This point of access does not contain cleared personnel. This is defined by the following:

- An Internet connected network, regardless of other security measures

- Any single uncleared U.S. person

- A group of associated foreign nationals within a U.S. organization, such as a corporate office operated in a foreign country

- A foreign owned company servicing part of the supply chain

- Any number of foreign nationals from a high threat country or its allies with access to some part of the FPGA supply chain

For a mitigation based on access to be effective, it needs to raise the access required to carry out the attack to one necessitating multiple points of access or complex points of access. For example, the access mitigation could result in an attack needing access from differing areas of the supply chain or by multiple personnel in an area of the supply chain.

- Technology Existing public technology means that an attack can be conducted using tools that are already available in the public or commercial domain, or are straightforward advances of public technology. Examples would include:

- Development tools provided by FPGA vendors

- Internal debugging features that are capable of changing device configuration

- Lab equipment used as intended

- Publicly available open source projects

- Published academic research

- Results of U.S. Government (USG) Research & Development (R&D) investment at the unclassified level, even when protected by International Traffic in Arms Regulations

For a mitigation based on technological complexity to be effective, it must increase the level of technology needed to carry out the attack to that which is beyond what can be found in the public domain. The most common method to achieve this mitigation is to apply cryptographic authentication based on USG standards.

Investment – Minimal investment of resources means that an attack requires

a team with existing FPGA knowledge and skills and individuals with domain

knowledge in the technology area of the system being assured. Minimal

resources are defined as any effort consisting of less than six person-years of

FPGA/domain expertise focused solely on attacking the target of interest.

For a mitigation based on investment of resources to be effective, it must force the attacker to expend greater resources in the form of engaging a complex interdisciplinary team comprised of a mix of specialties that are outside of the application design domain and FPGA technology to carry out an attack. Additionally, the mitigation would lengthen the time necessary to develop the attack to more than six person-years. Obfuscation of design data is not considered effective in this context. Common use of obfuscation has historically led to technological development in those additional disciplines that quickly nullified the obfuscation.

Value of Effect – Attacks that disable or subvert capabilities enable an

adversary to remove a capability from service or cause it to perform specific

deleterious actions. When combined with high targetability, these represent the

worst-case scenario for a failure of hardware assurance: enabling an adversary

to take over or disable capabilities on command.

For a mitigation based upon value of effect to the adversary, it must constrain the severity of the outcome on the target to one of lesser effect.

• Targetability - Inherently targetable and controllable threat operations are executed in a way that provides straightforward means to understand and predict the effect of an attack, and also provide a mechanism to control or time the attack. For example, an adversary with the ability to introduce new code into a system design can implement a broad number of malicious functions. A denial of service attack falls in this category, if and only if, it is possible for the adversary to control when it takes effect after the device is fielded. However, a simple reduction in reliability not tied to any trigger, which therefore cannot be controlled or timed in a planned way, does not fall in this category.

For a mitigation based on targetability to be effective, it must prevent the attack from being controlled effectively. That is, it must prevent the FPGA device from being used to attack a specific target at a specific time with a controllable trigger. This can be accomplished by performing mitigations that specifically target opportunities for communication.

For a program to achieve Level of Assurance 1, it must provide mitigations against threats that fall within these characteristics. LoA1 addresses threats that originate from an adversary whose intent is malicious and does not cover commercial assurance risks, such as re-marked parts. Economically motivated assurance threats have reliability risks associated with them. These threats should be addressed by the reliability testing of a program. For programs with stringent or specific reliability requirements, it is strongly recommended that the appropriate level of testing be conducted to ensure the proper operation of the product rather than relying on assurance mitigations. However, all programs with radiation-hardened requirements are an exception and in almost all cases should mitigated at a Level of Assurance 2 or Level of Assurance 3.

The following table lists the nine FPGA threats that are addressed by LoA1. Each threat is explained and accompanied by examples in more detail within the JFAC *FPGA Best Practices – Threat Catalog.*

Table 1: LoA1 threats

| #     | Threat description (TD)                                           |

|-------|-------------------------------------------------------------------|

| TD 1  | Adversary utilizes a known FPGA platform vulnerability            |

| TD 2  | Adversary inserts malicious counterfeit                           |

| TD 3  | Adversary compromises application design cycle                    |

| TD 4  | Adversary compromises system assembly, keying, or provisioning    |

| TD 5  | Adversary compromises third-party soft intellectual property (IP) |

| TD 6  | Adversary swaps configuration file on target                      |

| TD 7  | Adversary substitutes modified FPGA software design suite         |

| TD 8* | Adversary modifies FPGA platform family at design                 |

| TD 9  | Adversary compromises single-board computing system (SBCS)        |

<sup>\*</sup>TD 8 does not become a relevant threat until LoA2; however, JFAC requires LoA1 programs to answer an information query required by TD8 mitigations.

Each threat listed here has corresponding mitigations. These mitigations are derived from various commercial/government standards and existing best practices. The use of these standards and best practices should not preclude the use of any other standards or best practices. In particular, DoD projects identified as National Security Systems (NSS) should utilize the appropriate guidance as required by the Committee on National Security Systems (CNSS).

# 3.1 Complementary standards and guidance

Microelectronic quantifiable assurance (MQA) standards are intended to be complementary to other government and industry recognized risk management practices and standards. The following are standards for various mitigations:

National Institute of Standards and Technology (NIST) Federal Information Processing Standards Publication (FIPS) 186 Digital Signature Standard

- NIST FIPS 198 The Keyed-Hash Message Authentication Code (HMAC)

- NIST Special Publication (SP) 800-53 Security and Privacy Controls for Federal Information Systems and Organizations

- NIST SP 800-57 Recommendation for Key Management

- The Configuration Management section of NIST SP 800-60 Systems Security Engineering: Considerations for a Multidisciplinary Approach in the Engineering of Trustworthy Secure Systems

- NIST SP 800-171 Protecting Controlled Unclassified Information in Nonfederal Systems and Organizations

- NIST SP 800-172 Enhanced Security Requirements for Protecting Controlled Unclassified Information

- Committee on National Security Systems (CNSS) Policies

- SAE International AS6171 Test Methods Standard; General Requirements, Suspect/Counterfeit, Electrical, Electronic and Electromechanical Parts

- Trusted Systems and Network (TSN) Analysis

- Defense Acquisition Guidebook Chapter Nine Program Protection Plan

- DoD guidance for storage of Secret materials can be found in DODM 5200.01-V3.

- JFAC FPGA Best Practices Documents contact JFAC for available documents to support implementation practices for the FPGA standards in this guide.

Program offices should review and adhere to the standards provided in each document, as applicable. Additionally, programs are encouraged to apply applicable standards in addition to the standards described in this document.

#### 3.2 Exclusions

This FPGA Level of Assurance 1 Best Practice guide does **not** address the following concerns:

Non-malicious and profit driven reliability risks, such as re-marked parts.

Programs are responsible for establishing and enforcing system reliability requirements. However, compliance to SAE International AS6171 Test Methods Standard: General Requirements Suspect/Counterfeit, Electrical, Electronic and

Electromechanical Parts as recommended by this report is an effective detection mechanism for these kinds of counterfeit parts.

Threats to the confidentiality of the application design. The program application

can be loaded apart from the manufacturing process and under the protection

and oversight of the program. Confidentiality is preserved using existing

engineering practices, bitstream encryption, and other anti-tamper practices. For

more guidance in this area, see the DoD's Anti-tamper Executive Agent

(<a href="https://at.dod.mil">https://at.dod.mil</a>).

#### 3.3 Document use

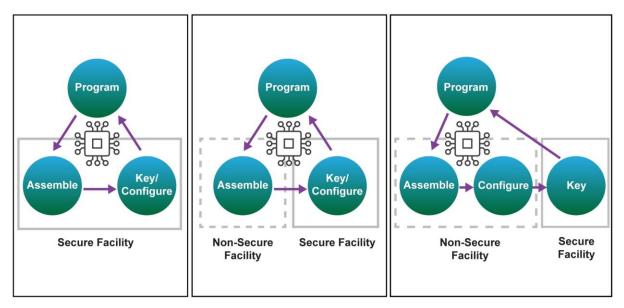

These FPGA assurance best practices instruct programs on protecting manufacturing and provisioning processes from adversarial influence. Specifically, they apply to the manufacturing, acquisition, programming, and first attachment of the FPGA devices. The program should define its own protection methods as boards become integrated into subcomponents, components, and then final systems.

For LoA1 compliance, each program should perform each mitigation listed in the "TD # Mitigations" sections. The "Mitigation Descriptions" sections provide details for each mitigation. In some cases, the full description contains additional options that are required to be LoA1 compliant. An asterisk "\*" next to any mitigation indicates additional options should be implemented.

When mitigations for all the threats listed under LoA1 are completed, that device can be said to have achieved LoA1. However, compliance with LoA1 can be impacted by changes in several areas during the system's life.

The Program Protection Plan (PPP) emphasizes the need to maintain and update protection measures throughout the lifecycle of a program. It is strongly recommended that each program identify events that would trigger a review of the PPP and hardware assurance practices after fielding. These events should include but not be limited to:

- Changes to the system,

- Changes to the supplier of critical components including the FPGA devices,

- Changes to the FPGA design software (new releases, fixes, etc.),

- Changes to the threat environment, and

- Revelations of new vulnerabilities to the FPGA devices.

The PPP documents list resources with which the program can track the latest available intelligence on threats and supply chain vulnerabilities. It is recommended that changes in any of these areas should prompt a review of the most up-to-date assurance mitigations against the triggering event. If threats or vulnerabilities threaten the system, it is recommended that new mitigations should be implemented to remain compliant to LoA1. Absent any changes in these areas, the devices should be considered to have achieved LoA1.

#### 3.4 General Comments on Mitigations

- Programs are encouraged to own as much of the fabrication process as possible and avoid third parties to the fullest extent possible.

- When third party sources are required, programs are encouraged to diversify their supply sources to minimize malicious targeting.

- Programs are encouraged to utilize cleared personnel and classified resources to the fullest extent possible.

- Programs are encouraged to use verification of all manufacturing steps to the fullest extent possible.

# 4. Threat Descriptions (TD)

# TD 1: Adversary utilizes a known FPGA platform vulnerability

In this attack, a foreign adversary utilizes a vulnerability in an FPGA platform or vendor development software package to initiate an attack. At LoA1, a vulnerability is an unclassified published weakness or vulnerability in the design of a specific FPGA platform or software program that would allow the attacker the ability to use it for malicious purposes.

Vulnerabilities could allow for leakage of sensitive information or keys; compromise of security or tamper detection functions; or unauthorized reconfiguration of the product. Unclassified and public vulnerabilities are published in various places, including vendor advisories, errata bulletins, and databases, such as those listed in the "Research Vulnerabilities" mitigation below. This threat can be introduced by a program not performing vulnerability research, an insider not disclosing the fact of the vulnerability

such that it may be used for nefarious purposes or adding/modifying design features for use with or triggering the vulnerability.

#### **TD 1 mitigations**

- <u>Use caution when selecting tools or platforms</u>. When possible do not select tools

or platforms that are end-of-life or beta/initial releases. Also, ensure known

vulnerabilities in tools/platforms have been adequately addressed in newer

releases.

- \*Research vulnerabilities affecting tools/platforms.

- <u>Use a revision control/version management system</u> that includes document/data control, document/data release, backups and archives, refresh of backup media, software, test equipment, and test environment.

- <u>Enforce auditability</u> of the application requirements, architecture, design, code, tests, bugs, and fixes. At a minimum, audit data should include what decisions were made, by whom, for what reason, and on what date.

- Perform a vulnerability data review.

- <u>Perform routine employment monitoring</u> to unmask a compromised insider who might hide the existence of a vulnerability.

- \*Take action to <u>prevent a compromised insider</u> from hiding a vulnerability.

# TD 1 mitigation descriptions

#### Use caution when selecting tools or platforms

Consider the longevity of selected tools and FPGA platforms. Newly released devices may not yet have a vulnerability history. Programs should proceed with caution when using newly released devices. End-of-life devices may not have support to mitigate vulnerabilities once identified.

In general, JFAC recommends programs use more modern device families when possible. These families possess more mature design architectures that encompass vulnerability fixes and advanced assurance features.

#### Research vulnerabilities

Research the respective FPGA platform and software for existing vulnerabilities in databases such as:

- Common Vulnerabilities and Exposures (CVE) <a href="https://cve.mitre.org">https://cve.mitre.org</a>

- Common Weakness Enumeration (CWE) <a href="https://cwe.mitre.org">https://cwe.mitre.org</a>

- NIST National Vulnerability Database (NVD) <a href="https://nvd.nist.gov">https://nvd.nist.gov</a>

- Government Industry Data Exchange Program (GIDEP) https://www.gidep.org/products/products.htm

- DISA Security Technical Implementation Guides (STIGs) https://public.cyber.mil/stigs/

- Searches for vendor advisories, errata bulletins, publications, and academic papers detailing vulnerabilities in the device in question.

If vulnerabilities are found in the FPGA device, **choose one** of the following options:

**Option 1:** Select a different FPGA platform device or software that does not have published vulnerabilities and that meets the program requirements.

**Option 2:** Use standard formal processes and procedures to work with the vendor to resolve the vulnerability. Once a fix is identified, only accept formal releases, do not accept custom beta fixes, custom patches, etc. for incorporation.

**Option 3:** The program can internally determine the vulnerability poses no significant risk to their product. JFAC is available to provide assistance in assessing the risk that the vulnerability poses to the system and acquire recommended mitigations for a particular vulnerability.

Note: If a vulnerability is identified, it is recommended to report it to Government Industry Data Exchange Program (GIDEP) and to contact the vendor so they may correct it.

#### Use a revision control/version management system

To prevent vulnerable software from being loaded into the environment, it is important that robust configuration management and revision management systems are in place. Before any version is installed, research should be performed for any known

vulnerabilities, how they have been addressed, and their impacts and vulnerabilities. Only authorized changes are allowable. All changes to the system or artifacts should be documented, approved, and auditable.

These systems should fulfill the following requirements:

- Allow only authorized system administrators to make changes to the underlying revision control tool and underlying server.

- Use a backup system that syncs to the primary and is maintained by a separate administrator. Each system should be managed by separate system administrators.

- Enforce administrative restrictions; restrict privileged access to only an authorized set of administrators; limit what users can do to the database; ensure all users are verified; encrypt database information—both in transit and at rest; enforce secure passwords; introduce role-based access control and privileges; and remove unused accounts.

- Remove any components or functions that are not necessary (for example, remove all sample files and default passwords).

- Ensure the system provides a complete and immutable, long-term change history

of every file. The system should log every change made by individuals. This

includes changes such as creating and deleting files and editing content. The

history should identify the person who made the change, what was changed, the

date of the change, and the purpose of the change.

- Ensure the system stores a reliable copy of assets that are currently in production.

- Ensure the system stores reliable copies of previous production versions of assets, allowing for the complete retrieval of those versions.

- Ensure password best practices (password rotation, length, etc.) are enforced. In lieu of a password, two-factor authentication can be utilized.

- All changes to the system or artifacts should be documented, approved, and auditable.

#### **Enforce auditability**

Enforce auditability of the requirements, architecture, design, code, tests, bugs, and fixes. At a minimum, audit data includes what decisions were made, by whom, for what reason, and on what date.

#### Perform a vulnerability data review

To prevent a compromised insider from hiding a vulnerability, ensure all critical activities are identified and documented. Ensure the entire design is reviewed by multiple people or a cleared individual. The original designer should not be the responsible party for performing the review. The reviewers should assess all vulnerability activities, including identification of vulnerabilities and the appropriateness of the mitigations.

#### Perform routine employment monitoring

Perform routine employment monitoring in which employee work patterns are observed. Patterns to look for include hostility toward other employees, late or excessive missing work, unexplained work outside normal work hours, and declining performance.

#### Prevent a compromised insider

To limit the potential effects of a compromised insider, select one of the following options:

**Option 1:** Ensure all critical activities are identified and documented. Independent third-party reviewers should assess all vulnerability activities, including identification of vulnerabilities and whether the appropriate mitigations are in place. **Note:** For LoA1, independent is defined as "not the originator". The reviewer can be on the same team if necessary.

**Option 2:** Perform designated work using personnel with at least a Secret-level clearance.

# **TD 2: Adversary inserts malicious counterfeit**

At LoA1, this threat assumes that the adversary already has access to an *existing* fabrication process for manufacturing counterfeits. Using this access, the adversary inserts additional logic in the FPGA die for their malicious purposes. In general, modifications to an FPGA design during the fabrication phase are considered to require a high effort. However, in cases where an adversary is known to have already counterfeited a device, that effort has already been invested and is thus reduced.

Explicitly, this threat is only of a counterfeit that contains functional differences that are security relevant.

While commercial (non-malicious) counterfeits, such as re-marked parts, may represent a reliability risk, they are not included under this level of assurance. Those counterfeits are not malicious by design, not controllable/targetable, and are economic in nature. Programs with specific reliability requirements should plan for the appropriate level of testing to verify that their design and components meet those goals. The exception to this statement are parts that have radiation-hardening requirements. In all cases, these devices should comply with Level of Assurance 2 or Level of Assurance 3 in addition to the appropriate level of reliability testing to secure the operation of their design.

The insertion of counterfeit parts can happen during any part of a device's lifecycle. This includes prior to purchase, during transit, while in storage by the program, during assembly, and at distribution prior to fielding.

JFAC relies on substantial physical device inspection to address these threats because the program has no positive control over the fabrication facility or its processes. Most of the FPGA fabrication facilities are foreign owned, not aligned to the goals of the United States, and not controllable by the program or DoD. JFAC can identify numerous "technically feasible" attacks for all fabrication countermeasures considered. Overlapping personnel and multi-party review in the verification process along with cryptographically protected IDs and reliability testing of sampled devices provides additional assurance protections.

Guidelines for conducting physical inspection are provided by the SAE AS6171 counterfeit detection standard. These guidelines are organized into "slash sheets." Each slash sheet is a description of a singular type of inspection process. For the purposes of this document, the slash sheets may be divided into several purposes:

- Slash sheets 2-10: describe physical inspections able to identify devices that were manufactured in an unauthorized fab.

- Slash sheet 11: describes physical inspections able to identify maliciously altered devices that were manufactured in an authorized fab.

- Slash sheets 3, 4, 6, 10: describe physical inspections intended to uncover malicious alterations made to the package internals of an authentic device.

More details regarding the physical inspection process are outlined in the mitigations below.

#### **TD 2 mitigations**

- For DoD system owners, <u>purchase from DoD authorized vendors and</u> <u>distributors</u>. The DoD program acquisition group can provide this information.

- Follow storage and shipping guidance for classified Secret or Trust Category I

materials when storing and transferring FPGA devices between locations.

- Validate the authenticity of the FPGA device.

#### TD 2 mitigation descriptions

#### Purchase from DoD authorized vendors and distributors

For DoD system owners, utilize DoD authorized vendors and distributors for all purchases. Authorized vendors can be identified through the acquisition organization.

#### Follow storage and shipping guidance

The program should document, maintain, and enforce both device storage and shipping procedures. Minimally, the procedures should enforce the verification and acceptance testing of all devices upon receipt. In addition to device verification, storage and shipping processes should focus on preventing and detecting adversary access to the parts. Access controls should be designed to thwart those seeking to alter or replace the devices while in storage or shipping.

#### **Storage protections** should include the following characteristics:

- Production devices should be stored and maintained in a restricted area separate from non-production devices (i.e., ones for design, test, etc.).

- The restricted area should enforce access controls that limit access to only those

personnel who require access to support direct job responsibilities. This

should exclude all members of the design team.

- All accesses to the restricted area should be recorded and audited.

- The FPGA devices should be audited on a regular cadence to ensure they have not been removed or modified.

- Production devices should be continuously tracked to include arrival of the device by unique identifier, interaction anyone has with the device, and exit of the device from inventory.

- The restricted area should have a clearly defined perimeter, but physical barriers are not required.

- Personnel within the area should be responsible for challenging all persons who may lack appropriate access. Accesses to the restricted area should be audited to include data containing who entered/exited the area, with a timestamp, and reason for entry.

- When possible, the FPGA devices should be stored within a tamper detection seal or tape to detect unauthorized access.

#### **Shipping protections** should include the following characteristics:

- Following acceptance testing, non-configured and non-keyed devices should be

using a commercial carrier that has been approved by the appropriate Cognizant

Security Agency (CSA) to transport Secret shipments, although the material is not

Secret. Commercial carriers may be used only within and between the 48

contiguous States and the District of Columbia or wholly within Alaska, Hawaii,

Puerto Rico, or a U.S. possession or trust territory.

- Utilize protections against pilferage, theft, and compromise, including:

- Hardened containers

- Tamper detection seals and tapes. The seals should be numbered, and the numbers indicated on all copies of the bill of lading (BL). When seals are used, the BL should be annotated substantially as follows:

- DO NOT BREAK SEALS EXCEPT IN CASE OF EMERGENCY OR UPON PRIOR AUTHORITY OF THE CONSIGNOR OR CONSIGNEE. IF FOUND BROKEN OR IF BROKEN FOR EMERGENCY REASONS, APPLY CARRIER'S SEALS AS SOON AS POSSIBLE AND IMMEDIATELY NOTIFY BOTH THE CONSIGNOR AND THE CONSIGNEE.

- Closely track shipment times and depot stops. Packages that are late should be considered suspect.

#### Validate the authenticity of the FPGA device

To validate the authenticity of the FPGA devices, choose one of the following options (descriptions are below):

**Option 1:** Use an FPGA device that includes a <u>cryptographically secure ID</u> that can be vendor verified.

**Option 2:** Perform <u>physical analysis</u> on a random sampling of devices to detect counterfeit parts.

#### Cryptographically secure identifier

For LoA1, the program should utilize an FPGA device that incorporates a cryptographically protected ID that can be verified against information sent by the vendor (not the authorized distributor). The use of this type of device ID mitigates the sub-threat of counterfeit parts made in an existing, non-authorized fabrication facility. While the specifics of each FPGA vendor and platform vary, many newer FPGA platforms contain this type of anti-counterfeiting feature. When these features are sufficiently secure, such mechanisms provide an extremely cost-effective method to detect counterfeits both at acquisition and throughout the FPGA device's lifecycle in a system. The two biggest advantages of such techniques are the ability to validate a device remotely and the ability to non-destructively re-validate a device at any time.

In contrast to physical anti-counterfeiting techniques, properly implemented cryptographic identifiers do not require destructive analysis for verification. A typical scheme could validate such a device simply by placing it in a socket. A design can facilitate access to the identifier through local access, such as a board header, or remotely. Depending on the exact mitigations selected, this potentially saves two distinct destructive steps: one at acquisition of the devices and one after assembly of the printed circuit board (PCB).

This kind of validation is where details matter, each FPGA vendor offers a unique approach, and each FPGA platform offers a unique variation. In no case is a fully readable ID acceptable. Instead, these schemes all detail cases where the device possesses a specific private cryptographic key. The device ID in this scheme can be cloned only if an adversary is able to get access to that private key. Regardless of the specific platform used, the public keys/identifiers of the devices being authenticated should be delivered and maintained in a secure way. For delivery, the vendor should

provide this information to the program using a NIST approved authentication algorithm to transmit the data. Examples would be an ECC-signed email with a verified certificate, or an https-based file distribution system using a verified certificate. Once received, the integrity of that list should be maintained by storing with protections appropriate to Critical Protected Information (CPI). This should include restricted role-based access on a network that is compliant with the contract defined Cybersecurity Maturity Model Certification (CMMC) level.

Specific criteria required for an appropriate device ID to support anti-counterfeiting are below:

- Cryptographically protected IDs utilize a private asymmetric key for which no read function exists. This should use a National Institute of Standards and Technology (NIST) approved asymmetric authentication algorithm.

- The provenance of the key should be understood in detail.

- The device should be able to authenticate a nonce using this key. Each device's ID should be authenticated by the vendor-provided public key through decryption of the nonce.

#### Physical analysis

Perform physical analysis on a sampling of random devices to detect counterfeit parts. This analysis applies specific, industry standard counterfeit inspection techniques, including package analysis, x-ray of the part, and examination of the die with comparisons against FPGA vendor-provided golden samples. This physical analysis is intended to catch parts that have been remarked or contain counterfeit die. The details of what steps to conduct in the analysis and recommendations on how to execute them are contained in the commercial standard document, SAE Test Methods Standard; General Requirements, Suspect/Counterfeit, Electrical, Electronic, and Electromechanical Parts, AS6171. These inspections should be carried out by cleared persons at a Secret level or higher or a lab independent of the program or its performers.

Physical analysis is a sequence of device analysis steps, from least destructive to most destructive, designed to ensure that the part in question is authentic. If a device fails a given step, it is not authentic, and there is no need to complete further steps. If all steps are completed and the device passes, it is likely authentic, with likelihood commensurate with the amount of effort it would take to get a counterfeit device to pass

these tests, subject to LoA1 criteria. Each AS6171 test is detailed in a separate document called a "slash sheet". Listed below are the slash sheets that comprise the standard. Users should ensure to use the latest version of AS6171 and associated slash sheets.

Table 2: List of AS6171 slash sheets

| Test Number | Description                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AS6171      | Test Methods Standard; General Requirements, Suspect/Counterfeit, Electrical, Electronic, and Electromechanical Parts                                      |

| AS6171/1    | Suspect/Counterfeit Test Evaluation Method                                                                                                                 |

| AS6171/2    | Techniques for Suspect/Counterfeit EEE Parts Detection by External Visual Inspection, Remarking and Resurfacing, and Surface Texture Analysis Test Methods |

| AS6171/3    | Techniques for Suspect/Counterfeit EEE Parts Detection by X-ray Fluorescence Test Methods                                                                  |

| AS6171/4    | Techniques for Suspect/Counterfeit EEE Parts Detection by Delid/Decapsulation Physical Analysis Test Methods                                               |

| AS6171/5    | Techniques for Suspect/Counterfeit EEE Parts Detection by Radiological Test Methods                                                                        |

| AS6171/6    | Techniques for Suspect/Counterfeit EEE Parts Detection by Acoustic Microscopy (AM) Test Methods                                                            |

| AS6171/7    | Techniques for Suspect/Counterfeit EEE Parts Detection by Electrical Test Methods                                                                          |

| AS6171/8    | Techniques for Suspect/Counterfeit EEE Parts Detection by Raman Spectroscopy Test Methods                                                                  |

| AS6171/9    | Techniques for Suspect/Counterfeit EEE Parts Detection by Fourier Transform Infrared Spectroscopy (FTIR) Test Methods                                      |

| AS6171/10   | Techniques for Suspect/Counterfeit EEE Parts Detection by Thermogravimetric Analysis (TGA) Test Methods                                                    |

| AS6171/11   | Techniques for Suspect/Counterfeit EEE Parts Detection by Design Recovery Test Methods                                                                     |

For the purposes of LoA1, the program should follow the lot sampling guidelines found in the AS6171 document and exercise the tests defined by slash sheets 1-10. The tests defined in slash sheet 11 are not necessary for LoA1 but will become more important at higher assurance levels. The waiving of slash sheet 11 testing for LoA1 does not supersede any other DoD standard that requires it.

#### Select sample parts

The selection of parts to be physically sampled should be handled in such a way that a compromised insider could not knowingly select only genuine parts to be sampled. Possible sampling options include the following:

**Option 1:** An independent party handles part selection before shipping. They should physically verify that the parts selected make it all the way to the physical inspection processes and verify upon receipt that the right parts were received.

**Option 2:** Use a non-human random selection automated process for sampling.

**Option 3:** Physical verification and sampling work should be conducted by personnel holding clearances of at least the Secret level and carried out in facilities cleared to at least the Secret level.

## TD 3: Adversary compromises application design cycle

In this threat, a compromised insider has access to the design process and data related to an FPGA application development effort. This insider can use their access to modify design code, design constraints, or FPGA configuration settings, or swap in a distinct configuration file that is authenticated and built with the same tools and keys being used by the design team. The actor is in a particularly advantageous position because they can modify the product during any phase of the design process. This same threat surface may also be attacked via remote network intrusion. An attacker with network access may also be able to modify important design data in a way that introduces a Trojan or other nefarious function.

As TD 3 is comprised of numerous scenarios, this threat is broken into eight sub-threats or scenarios and addressed separately. Collectively, these scenarios describe the entire threat at TD 3 and each of the mitigations for each scenario should be implemented. The specific scenarios are as follows:

Introduction of a compromised design into the application,

- Modification of test benches or plans to reduce coverage or hide Trojan code,

- Introduction of a Trojan into the application design during development,

- Introduction of compromised tooling or software into the environment,

- Network intrusion,

- Compromised employee,

- Modification of revision control that hides code or test bench modification (associated mitigations are captured in the "in all cases" section below), and

- Introduction of modified configuration data after generation (associated mitigations are captured in the "in all cases" section below).

#### **TD 3 mitigations**

The best practices presented here do not describe a standalone engineering FPGA design flow, but rather the assurance practices that should be integrated into the existing design procedures. These assurance practices incorporate industry-accepted design best practices with emphasis on documented and approved design, review, and test procedures.

TD 3 mitigations focus strongly on the insider threat. At LoA1, access is defined as singular with uncleared people. As such, this threat can be mitigated by following the guidance in the <u>use cleared personnel in a cleared environment</u> section. In the event that is not possible, the mitigations associated with each scenario should be incorporated.

#### Use cleared personnel in a cleared environment

Use cleared personnel with at least a Secret-level clearance in an environment suitable for a network cleared at the Secret level.

When the program selects not to use cleared personnel and a cleared environment, they should implement all TD 3 sub-threat mitigations, as there are multiple threats to be mitigated. The following mitigations are applicable to all the sub-threats identified in this section:

Track critical data in a revision control system.

- <u>Enforce auditability</u> of the requirements, architecture, design, code, tests, bugs, and fixes. At a minimum, audit data includes what decisions were made, by whom, for what reason, and on what date.

- Use a revision control/version management system that meets the requirements described later in this section.

#### TD 3 mitigation descriptions

#### Track critical data in a revision control system

The program should identify and document all data that is considered critical. Each critical data item should be stored and tracked in the revision control system. Minimally, the following documents, data artifacts, and tool configurations should be managed in the revision control system:

- Third-party IP (3PIP)

- Utilized libraries

- Development files, code, software used for development, synthesis scripts, and tools

- Test benches, test plans, test procedures, and test reports

- Tool configuration settings

- Design documents

#### **Enforce auditability**

Enforce auditability of the requirements, architecture, design, code, tests, bugs, and fixes. At a minimum, audit data includes what decisions were made, by whom, for what reason, and on what date.

#### Use a revision control/version management system

Revision control/version management systems should meet the following requirements:

- Allow only authorized system administrators to make changes to the underlying revision control tool and underlying server.

- Implement a backup system that mimics the primary system and is maintained by a separate administrator. Separate system administrators should manage each system.

- Enforce administrative restrictions; restrict privileged access to only an authorized set of administrators; limit what users can do to the database; ensure all users are verified; encrypt database information—both in transit and at rest; enforce secure passwords; introduce role-based access control and privileges; and remove unused accounts.

- Remove any components or functions that are not needed; for example, remove all sample files and default passwords.

- Ensure the system provides a complete and immutable long-term change history

of every file. The system should log every change made by individuals. This

includes creation and deletion of files and content edits. The history should

include the person who made the change, what was changed, the date, and

written notes on the purpose of each change.

- Ensure the system stores a reliable copy of assets that are currently in production.

- Ensure the system stores reliable copies of previous production versions of assets, allowing for the complete retrieval of those versions.

- Enforce password best practices (password rotation, length, etc.). In lieu of a password, two-factor authentication can be used.

# TD 3.1: Mitigating the introduction of a compromised design into the application

In this scenario, the adversary is able to insert a Trojan into the design after the design has been verified, but before the design is loaded for final deployment. Strict controls on the revision control system will help prevent the adversary from making unmonitored changes.

To accomplish this task, the adversary would have to compromise the revision management system. That compromise could allow the adversary to switch the verified configuration files, settings, hash or other pertinent information. To protect against this, the program should store and isolate the verified FPGA application configuration files, settings, and associated hash. Before the design is loaded for final deployment, the program should verify the hash to know the verified version is the same as what they want to deploy. For extra assurance, the program has all the necessary data to

reproduce the build which can be used to verify the stored versions against the reproduced version.

#### **Mitigations**

- Physically isolate and store the application design until it is delivered.

- Perform a reproducible build of the application.

#### **Descriptions**

#### Isolate and store the application design

To protect the application design after verification but before deployment, the final configuration file and hash should be physically isolated and stored until it is delivered for provisioning. Ensure the file can only be accessed via authentication of two distinct parties. No single individual should be able to access the files. The limited set of people with access should have to follow access control procedures such that access is controlled, monitored, logged, and auditable.

#### Perform a reproducible build

A reproducible build process is a methodology to verify the integrity of the FPGA synthesis and build software. Reproducible build performs the synthesis process taking in human readable HDL, and other human readable inputs, and consistently generates the same final configuration file (bitstream). At LoA1 reproducible builds should be performed using independently acquired software and installed independently on two distinct computers. It is expected that this process will, in most cases, require the use of the same version of the electronic design automation (EDA) tools, and, in some cases, the same operating system version. This process will highlight the possession of modified software when there is a mismatch. Contact the FPGA software vendors for more information on how to perform reproducible builds.

# TD 3.2: Mitigating the modification of test benches or plans to reduce coverage or hide Trojan code

In this threat, the adversary makes changes to the test bench to hide malicious code, reduce coverage, or reduce functionality.

#### **Mitigations**

- Create and <u>execute a documented test plan</u> that identifies the various test reviews that will take place, analysis to be performed, type of testing to be performed, and the methods used to accomplish the test.

- <u>Validate and verify test processes</u> which include design/test team separation, peer reviews, and use of automated tools where applicable.

- Ensure the test environment is maintained via configuration management as a critical system.

- Use a revision control/version management system.

#### **Descriptions**

#### Execute a documented test plan

The program should consider assurance when creating and maintaining the test plan. The test plan and processes should at least:

- Provide a mechanism to verify all requirements captured in the FPGA specification.

- Explicitly list code coverage metrics, the type of testing that will be performed, and acceptable testing guidelines. Code coverage should state how much code is checked by the test bench, providing information about dead code in the design and holes in the test suites. Document the decision to use/not use other types of testing, such as directed test, constrained random stimulus, and assertion.

- Ensure code coverage includes statement coverage, branch coverage, Finite

State Machine (FSM), condition, expression, and toggle coverage. Document

any code that will not be covered and why. Ensure untested code is documented

and reviewed through the review process. Use functional tests to verify the FPGA

does what it is supposed to do. Any deviations should be documented and

approved.

- Specify the verification environment which describes the tools, the software, and the equipment needed to perform the reviews, analysis, and tests. Each of these items should be maintained under revision control.

- Document and analyze unexpected behavior and final implementation conclusions.

- Ensure all test discrepancies, bugs, etc., are resolved via a change process.

#### Validate and verify test processes

The program should take care to ensure test processes consider assurance needs. This includes design/test team separation, peer reviews, and use of automated tools where applicable. All test discrepancies, bugs, etc., should be resolved via a change process utilizing a change management system. The established processes should be documented, enforced, and audited.

#### Ensure the test environment is maintained via configuration management

The test environment should be treated as a critical system and maintained similarly to the production environment.

#### Use a revision control/version management system

Revision control/version management systems should meet the following requirements:

- Allow only authorized system administrators to make changes to the underlying revision control tool and underlying server.

- Implement a backup system that mimics the primary system and is maintained by a separate administrator. Separate system administrators should manage each system.

- Enforce administrative restrictions; restrict privileged access to only an authorized set of administrators; limit what users can do to the database; ensure all users are verified; encrypt database information—both in transit and at rest; enforce secure passwords; introduce role-based access control and privileges; and remove unused accounts.

- Remove any components or functions that are not needed; for example, remove all sample files and default passwords.

- Ensure the system provides a complete and immutable long-term change history

of every file. The system should log every change made by individuals. This

includes creation and deletion of files and content edits. The history should

include the person who made the change, what was changed, the date, and

written notes on the purpose of each change.

- Ensure the system stores a reliable copy of assets that are currently in production.

- Ensure the system stores reliable copies of previous production versions of assets, allowing for the complete retrieval of those versions.

- Enforce password best practices (password rotation, length, etc.). In lieu of a password, two-factor authentication can be used.

# TD 3.3: Mitigating the introduction of a Trojan into the application design during development

In this scenario, malicious functionality is introduced into the application design during the development phase.

#### Mitigations

- Ensure all design artifacts have a direct bi-directional link to approved requirements. Tracing to design decisions is permitted in support of derived requirements.

- <u>Enforce peer review</u> best practices.

- Create and <u>execute a documented test plan</u>.

- <u>Implement, validate, and verify test processes</u> which include design/test team separation, peer reviews, and use of automated tools where applicable.

- <u>Select a formal "proof" process</u> that can validate the equivalency of the hardware descriptor language (HDL) and final configuration file. For more information on "proof" tools, contact JFAC.

#### **Descriptions**

# Ensure all design artifacts have a direct bi-directional link to approved requirements

All requirements should be documented and traced. Functionality that is not associated with a requirement should not be allowed.

#### **Enforce peer review**

Establish and enforce peer review practices with the following:

• The author and the reviewer should be different people.

- Ensure the design process has time allocated for code reviews.

- Code review should be done in parallel with development, reviewing small chunks at a time.

- Anyone reviewing the code should already be familiar with the agreed upon architecture.

- All black box portions of the design should be identified, justified, and approved.

- All scripts that produce design artifacts (HDL, netlist, etc.) should be reviewed and approved. Ensure there are no unexpected paths, filenames, or suppressed outputs.

- Ensure the code reviews, at a minimum, verify:

- The code does what it is intended to do.

- The code can be traced to requirements.

- The code is not needlessly complex.

- Coding standards are being utilized.

- No extraneous code exists, the developer is not implementing unapproved items that may have future utility.

- The code has appropriate unit tests.

- Tests are well designed.

- The code uses clear names for everything.

- Comments are clear and useful, and mostly explain "why" instead of "what".

#### Execute a documented test plan

The program should consider assurance when creating and maintaining the test plan. The test plan and processes should at least:

- Provide a mechanism to verify all requirements captured in the FPGA specification.

- Explicitly list code coverage metrics, the type of testing that will be performed, and acceptable testing guidelines. Code coverage should state how much code is checked by the test bench, providing information about dead code in the

design and holes in the test suites. Document the decision to use/not use other types of testing, such as directed test, constrained random stimulus, and assertion.

- Ensure code coverage includes statement coverage, branch coverage, Finite

State Machine (FSM), condition, expression, and toggle coverage. Document

any code that will not be covered and why. Ensure untested code is documented

and reviewed through the review process. Use functional tests to verify the FPGA

does what it is supposed to do. Any deviations should be documented and

approved.

- Specify the verification environment which describes the tools, the software, and the equipment needed to perform the reviews, analysis, and tests. Each of these items should be maintained under revision control.

- Document and analyze unexpected behavior and final implementation conclusions.

- Ensure all test discrepancies, bugs, etc., are resolved via a change process.

- All modifications made to the application should undergo full testing. Do not allow untested modifications to go to release.

## Implement, validate, and verify test processes

The program should take care to ensure test processes consider assurance needs. This includes design/test team separation, peer reviews, and use of automated tools where applicable. All test discrepancies, bugs, etc., should be resolved via a change process utilizing a change management system. The established processes should be documented, enforced, and audited

## Select a formal "proof" process

Use logical equivalency checking to the greatest extent possible. Equivalency checking is used to prove the tools did not modify the logic or configuration settings. To do this, the final bitstream is compared to the originating application HDL to demonstrate they are logically equivalent with no extraneous logic in the final format. This approach confirms Trojans were not inserted during the implementation steps. This check also confirms configuration settings are maintained and not altered. Configuration settings are those parameters included in the configuration file that affect the behavior of the FPGA device itself but are not a part of the program application. Examples would include tamper settings, JTAG settings, and key storage.

There are technical challenges associated with performing Logic Equivalence Check (LEC) on FPGA data. Contact JFAC for information on emerging industry tools that can assist in identifying configuration data in the FPGA formats or automate the creation of hints files.

# TD 3.4: Mitigating the introduction of compromised tooling or software into the environment

In this scenario, the adversary introduces compromised tooling or software into the environment. This can be accomplished by an insider or through network intrusion.

# **Mitigations**

- Accept only digitally signed software deliveries.

- Validate cryptographic hashes against vendor provided hashes.

- \*Research vulnerabilities affecting tools/platforms using commercial and JFAC-provided resources. If vulnerabilities are found, use an alternate or newer version that does not have the vulnerability. Alternatively, perform a risk assessment and coordinate findings with JFAC.

- <u>Use a revision control/version management system</u> that includes document/data control, document/data release, backups and archives, refresh of backup media, retention of tools and software, test equipment, and test environment.

- <u>Utilize a reproducible build process</u> to generate any deployable configuration files. The program should independently validate this reproducibility for each deployable version on a distinct computer system, with an independently acquired version of the same EDA tools.