# Joint Tactical Radio System Standard MHAL on Chip Bus Application Program Interface

Version: 1.1.5 26 June 2013

Statement A - Approved for public release; distribution is unlimited (17 July 2013).

i

# **Revision History**

| Version                                                                                                       | Description                                                           | <b>Last Modified Date</b> |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| 1.0.5                                                                                                         | Preparation for public release                                        | 29-Jun-2010               |

|                                                                                                               | ICWG Approved                                                         |                           |

| 1.1 <draft></draft>                                                                                           | .1 < Draft> -Added MOCB RF Coordinator (RFC) Extension                |                           |

|                                                                                                               | -Update Introduction, references, and Abbreviations in MOCB API       |                           |

| 1.1 <final draft=""></final>                                                                                  | No further changes                                                    | 01-Jun-2011               |

| 1.1.1 <draft></draft>                                                                                         | Delete section E.3.2 Scanning Function                                | 03-Aug-2011               |

|                                                                                                               | Delete Figure 35:MOCB Data Bus Structure                              |                           |

|                                                                                                               | Delete Figure 36: MOCB Waveform Initiator Functional Block Diagram    |                           |

|                                                                                                               | Delete Figure 37: Tx Enabled Rx Enabled Timing Diagram                |                           |

|                                                                                                               | Delete Table 7 - MOCB RFC Framework                                   |                           |

|                                                                                                               | Update Figure 34: MOCB Waveform Initiator Context Diagram             |                           |

|                                                                                                               | Update Table 7 MOCB Initiator Module I/O                              |                           |

|                                                                                                               | Update text throughout Section E. MOCB RF Chain Coordinator Extension |                           |

|                                                                                                               | Update E.3.1:Transmit Power Control Function: MOCBRFC_TPC             |                           |

|                                                                                                               | Update E.3.2:Rx Gain Function: MOCBRFC_RXGAIN                         |                           |

| 1.1.1 <final draft=""></final>                                                                                | Update Section 3.1.1 Parameters                                       | 29-Aug-2011               |

|                                                                                                               | Add additional clarification to Figure 10                             |                           |

|                                                                                                               | Remove contents from section 3.2.1.1 Module I/O                       |                           |

|                                                                                                               | Delete text from section 3.1 Transmit Power Control Function          |                           |

|                                                                                                               | Delete section E.3.2.3 Sample Interface                               |                           |

| 1.1.1 ICWG Approved                                                                                           |                                                                       | 31-Aug-2011               |

| 1.1.2 <draft> Add "nEntries" parameter to section C.3.1.3, C.3.1.4,C.3.1.7, C.3.1.8, C.5.4.4, C.5.4.5</draft> |                                                                       | 16-Nov-2011               |

| 1.1.2 <final draft=""></final>                                                                                | 1.1.2 <final draft=""> Misc. Redline changes</final>                  |                           |

| 1.1.2                                                                                                         | Misc. Redline changes                                                 | 24-Jan-2012               |

|                                                                                                               | ICWG Approved                                                         |                           |

| 1.1.3                                                                                                         | Misc. Redline changes                                                 | 18-Apr-2012               |

|                                                                                                               | ICWG Approved                                                         |                           |

Version: 1.1.5 26 June 2013

| Version                        | Description                                                | <b>Last Modified Date</b> |

|--------------------------------|------------------------------------------------------------|---------------------------|

| 1.1.4 <draft></draft>          | Change "read" operation to "mocbRead" in Section C.3.1.1   | 10-Jul-2012               |

|                                | Change "write" operation to "mocbWrite" in Section C.3.1.5 |                           |

| 1.1.4 <final draft=""></final> | No further changes                                         | 7-Aug-2012                |

| 1.1.4                          | No further changes                                         | 14-Aug-2012               |

|                                | ICWG Approved                                              |                           |

| 1.1.5                          | 1.1.5 Preparation for public release                       |                           |

|                                | ICWG Approved                                              |                           |

# **Table of Contents**

| A. MOCB                                          | 11  |

|--------------------------------------------------|-----|

| B. MOCB GPP API EXTENSION                        | 17  |

| C. MOCB DSP API EXTENSION                        | 60  |

| D. MOCB FPGA API EXTENSION                       | 96  |

| E. MOCB RF CHAIN COORDINATOR (RFC) API EXTENSION | 141 |

# **Table of Contents**

| A. MOCB                                    |    |

|--------------------------------------------|----|

| A.1 Introduction                           | 11 |

| A.1.1 Overview                             | 11 |

| A.1.2 Service Layer Description            |    |

| A.1.3 Referenced Documents                 |    |

| A.1.3.1 Government Documents               |    |

| A.2 Services                               | 13 |

| A.2.1 General Assumptions                  |    |

| A.2.2 Logical Destination (LD) Assumptions |    |

| A.3 Service Primitives and Attributes      |    |

| A.4 Interface Definitions                  | 14 |

| A.5 Data Types and Exceptions              | 14 |

| Appendix A.A – Abbreviations and Acronyms  |    |

| Appendix A.B – Performance Specification   |    |

|                                            |    |

| B. MOCB GPP API EXTENSION                  | 17 |

| B.1 Introduction                           | 17 |

| B.1.1 Overview                             |    |

| B.1.2 Service Layer Description            |    |

| B.1.2.1 MOCB Port Connections              |    |

| B.1.3 Modes of Service                     |    |

| B.1.4 Service States                       |    |

| B.1.4.1 MOCB State Diagram                 |    |

| B.1.5 Referenced Documents                 | 19 |

| B.1.5.1 Government Documents               | 19 |

| B.2 Services                               | 21 |

| B.2.1 Provide Services                     |    |

| B.2.2 Use Services                         | 22 |

| B.2.3 Interface Modules                    | 23 |

| B.2.3.1 MHAL::MOCB                         | 23 |

| B.2.4 Sequence Diagrams                    | 23 |

| B.3 Service Primitives and Attributes      | 24 |

| B.3.1 MHAL::MOCB::GPPMemoryAccessConsumer  | 24 |

| B.3.1.1 read Operation                     |    |

| B.3.1.2 readWait Operation                 | 26 |

| B.3.1.3 multiReadWait Operation            | 28 |

| B.3.1.4 multiLDReadWait Operation          | 30 |

| B.3.1.5 write Operation                    | 31 |

| B.3.1.6 writeWait Operation                |    |

| B.3.1.7 multiWriteWait Operation           |    |

| B.3.1.8 multiLDWriteWait Operation         |    |

| B.3.1.9 modify Operation                   |    |

| B.3.1.10 modifyWait Operation              | 40 |

| B.3.1.11 configLDMap Operation                                | 42  |

|---------------------------------------------------------------|-----|

| B.3.2 MHAL::MOCB::GPPEvent                                    |     |

| B.3.2.1 registerSemaphore Operation                           | 43  |

| B.3.2.2 unregisterSemaphore Operation                         |     |

| B.3.2.3 registerEventMux Operation                            |     |

| B.4 IDL                                                       | 48  |

| B.4.1 MOCB Device IDL                                         | 48  |

| B.5 UML                                                       | 52  |

| B.5.1 Data Types                                              | 53  |

| B.5.1.1 MultiRead                                             | 53  |

| B.5.1.2 MultiLDRead                                           | 53  |

| B.5.1.3 MultiWrite                                            | 53  |

| B.5.1.4 MultiLDWrite                                          | 53  |

| B.5.1.5 Map                                                   | 53  |

| B.5.2 Enumerations                                            | 53  |

| B.5.2.1 AddressIndexType                                      | 53  |

| B.5.2.2 ErrorCodes                                            | 54  |

| B.5.2.3 BitOp                                                 | 55  |

| B.5.3 Exceptions                                              | 56  |

| B.5.4 Structures                                              | 56  |

| B.5.4.1 MultiReadEntry                                        |     |

| B.5.4.2 MultiLDReadEntry                                      |     |

| B.5.4.3 MultiWriteEntry                                       |     |

| B.5.4.4 MultiLDWriteEntry                                     |     |

| B.5.4.5 MapEntry                                              |     |

| Appendix B.A – Abbreviations and Acronyms                     |     |

| Appendix B.B – Performance Specification                      | 59  |

| C MOCD DCD ADI EVERNICIONI                                    | (0  |

| C. MOCB DSP API EXTENSION                                     |     |

| C.1 Introduction                                              |     |

| C.1.1 Overview                                                |     |

| C.1.2 Service Layer Description                               |     |

| C.1.3 Referenced Documents                                    |     |

| C.2 Services                                                  |     |

| C.2.1 Interface Modules                                       |     |

| C.2.1.1 MOCB DSP Memory Access Consumer Interface Description |     |

| C.2.2 Sequence Diagrams                                       |     |

| C.3 Service Primitives and Attributes                         |     |

| C.3.1 DSPMemoryAccessConsumer                                 |     |

| C.3.1.2 readWait Operation                                    |     |

| C.3.1.3 multiReadWait Operation                               |     |

|                                                               |     |

| C.3.1.4 multiLDReadWait Operation                             |     |

| C.3.1.5 <i>mocbWrite</i> Operation                            |     |

| C.J.1.0 WHE WALL OPELANOH                                     | / 4 |

| C.3.1.7 multiWriteWait Operation                                                      | 76  |

|---------------------------------------------------------------------------------------|-----|

| C.3.1.8 multiLDWriteWait Operation                                                    | 78  |

| C.3.1.9 modify Operation                                                              | 79  |

| C.3.1.10 modifyWait Operation                                                         | 81  |

| C.3.1.11 configLDMap Operation                                                        | 83  |

| C.3.2 DSPEvent                                                                        |     |

| C.3.2.1 registerSemaphore Operation                                                   | 84  |

| C.3.2.2 unregisterSemaphore Operation                                                 |     |

| C.3.2.3 registerEventMux Operation                                                    |     |

| C.4 Interface Definitions                                                             |     |

| C.5 Data Types and Exceptions                                                         |     |

| C.5.1 Data Types                                                                      |     |

| C.5.2 Macros                                                                          |     |

| C.5.2.1 MOCBAddressIndexType                                                          |     |

| C.5.2.2 MOCBErrorCodes                                                                |     |

| C.5.2.3 MOCBBitOp                                                                     |     |

| C.5.3 Exceptions                                                                      |     |

| C.5.4 Structures                                                                      |     |

| C.5.4.1 MOCBMemoryDescriptor                                                          |     |

| C.5.4.2 MOCBMultiReadEntry                                                            |     |

| C.5.4.3 MOCBMultiLDReadEntry                                                          |     |

| C.5.4.4 MOCBMultiWriteEntry                                                           |     |

| C.5.4.5 MOCBMultiLDWriteEntry                                                         |     |

| C.5.4.6 MOCBMapEntry                                                                  |     |

| Appendix C.A – Abbreviations and Acronyms<br>Appendix C.B – Performance Specification |     |

| Appendix C.D – I error mance Specification                                            |     |

| D. MOCB FPGA API EXTENSION                                                            | 96  |

| D.1 Introduction                                                                      |     |

| D.1.1 Overview                                                                        |     |

| D.1.2 Service Layer Description                                                       |     |

| D.1.2.1 MOCB FPGA Signals                                                             |     |

| D.1.2.2 Data and Control Flow                                                         |     |

| D.1.2.3 MOCB Configuration Package                                                    | 108 |

| D.1.2.4 Translation Layer                                                             |     |

| D.1.2.5 MOCB FPGA Timing                                                              | 118 |

| D.1.3 Referenced Documents                                                            | 132 |

| D.1.3.1 Government Documents                                                          |     |

| D.2 Services                                                                          | 132 |

| D.3 Service Primitives and Attributes                                                 | 132 |

| D.4 Definitions                                                                       | 133 |

| D.4.1 Entity Definitions                                                              |     |

| D.4.1.1 Target Entity Description                                                     |     |

| D.4.1.2 Initiator Entity Description                                                  |     |

| D.4.2 Package definitions                                                             |     |

| D.4.2.1 Platform Description                       | 136 |

|----------------------------------------------------|-----|

| D.4.2.2 Waveform Description                       |     |

| D.5 Data Types and Exceptions                      |     |

| Appendix D.A – Abbreviations and Acronyms          |     |

| Appendix D.B – Performance Specification           |     |

| Appendix D.C – Clock Specification                 |     |

| Appendix 2.0 Clock Specification                   |     |

| E. MOCB RF CHAIN COORDINATOR (RFC) API EXTENSION   | 141 |

| E.1 Introduction                                   | 141 |

| E.1.1 Overview                                     |     |

| E.2 Services                                       | 142 |

| E.2.1 I/F Modules                                  | 142 |

| E.3 Service Primitives and Attributes              | 143 |

| E.3.1 Transmit Power Control Function: MOCBRFC_TPC | 143 |

| E.3.1.1 Parameters                                 | 143 |

| E.3.1.2 Events                                     | 144 |

| E.3.2 Rx Gain Function: MOCBRFC_RXGAIN             | 144 |

| E.3.2.1 Parameters                                 | 144 |

| E.3.2.2 Events                                     | 144 |

| E.4 Interface Definitions                          | 145 |

| E.5 Data types and Exceptions                      | 145 |

| Appendix E.A – Abbreviations and Acronyms          |     |

| Appendix E.B – Performance Specification           |     |

# **Lists of Figures**

| FIGURE 1 – LD EXAMPLE                                        | 13  |

|--------------------------------------------------------------|-----|

| FIGURE 2 – LD OFFSET EXAMPLE                                 | 14  |

| FIGURE 3 – MOCB PORT DIAGRAM                                 | 18  |

| FIGURE 4 – MOCB STATE DIAGRAM                                | 19  |

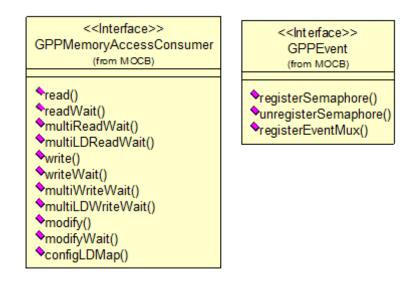

| FIGURE 5 – MOCB INTERFACE CLASS DIAGRAM                      | 23  |

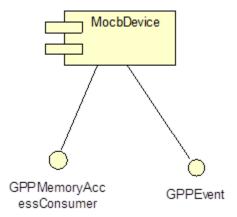

| FIGURE 6 – MOCB COMPONENT DIAGRAM                            | 52  |

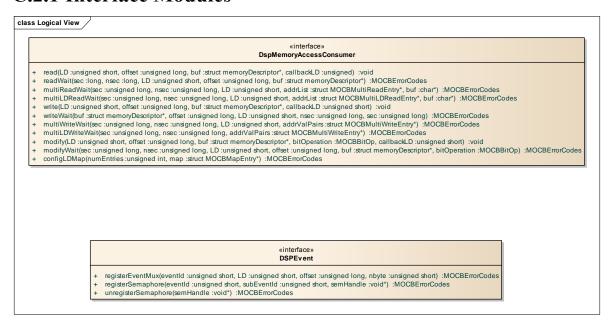

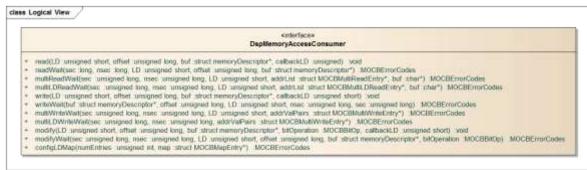

| FIGURE 7 – MOCB DSP INTERFACE DIAGRAM                        | 62  |

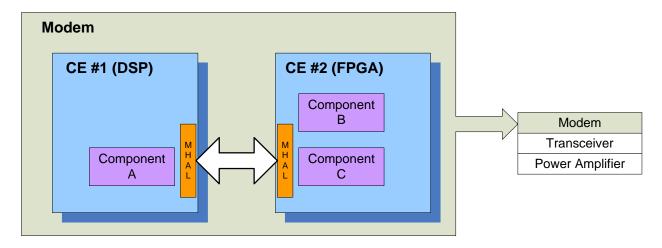

| FIGURE 8 – WAVEFORM COMPONENT ALLOCATION EXAMPLE             | 96  |

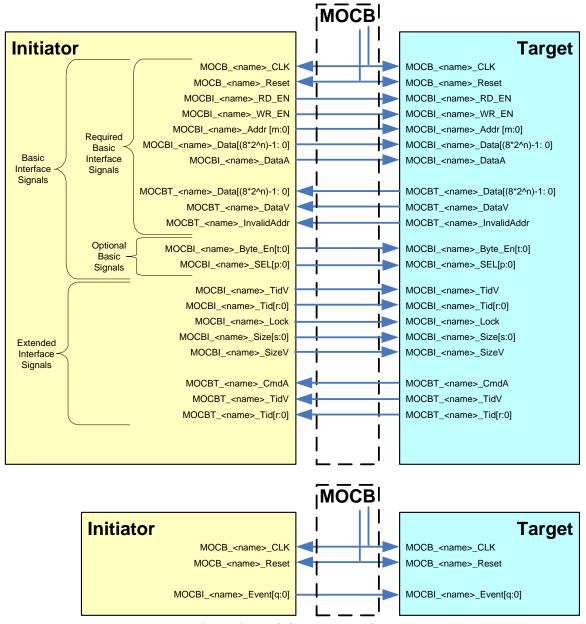

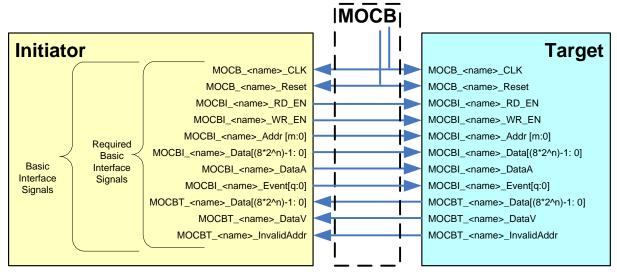

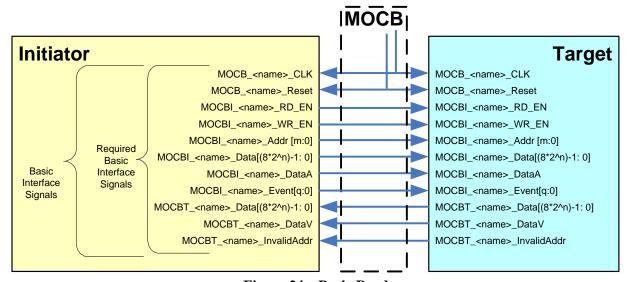

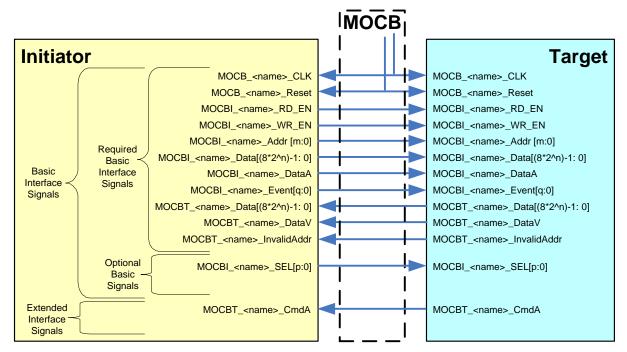

| FIGURE 9 – MOCB BUS INTERFACE                                | 97  |

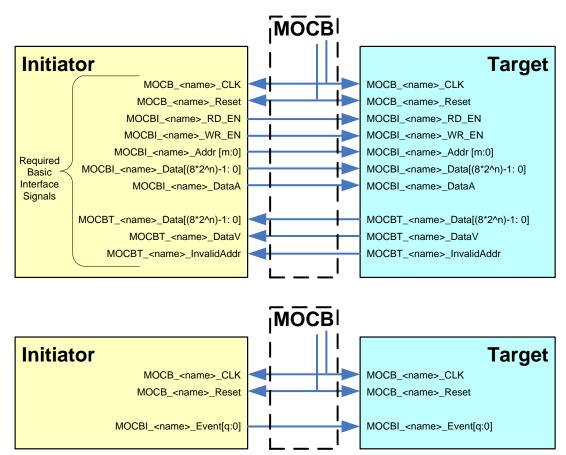

| FIGURE 10 - MOCB **REQUIRED BASIC BUS INTERFACE SIGNALS      | 102 |

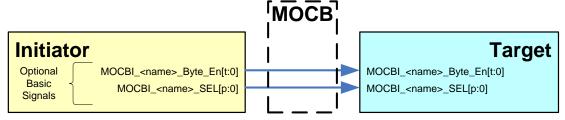

| FIGURE 11 – OPTIONAL BASIC SIGNALS                           | 103 |

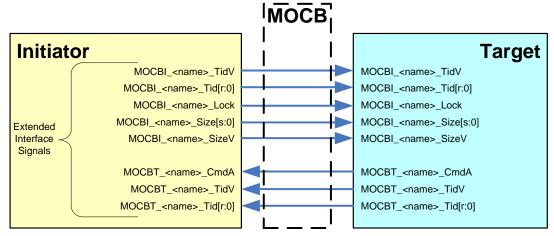

| FIGURE 12 – MOCB EXTENDED INTERFACE SIGNALS                  | 105 |

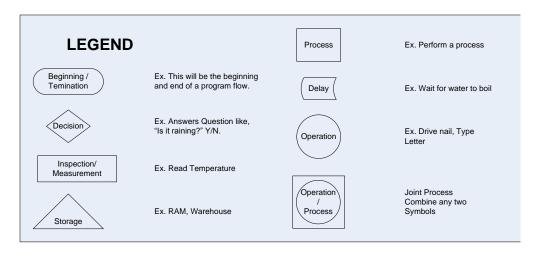

| FIGURE 13 – BASIC FLOWCHART STANDARD DEFINITIONS             | 106 |

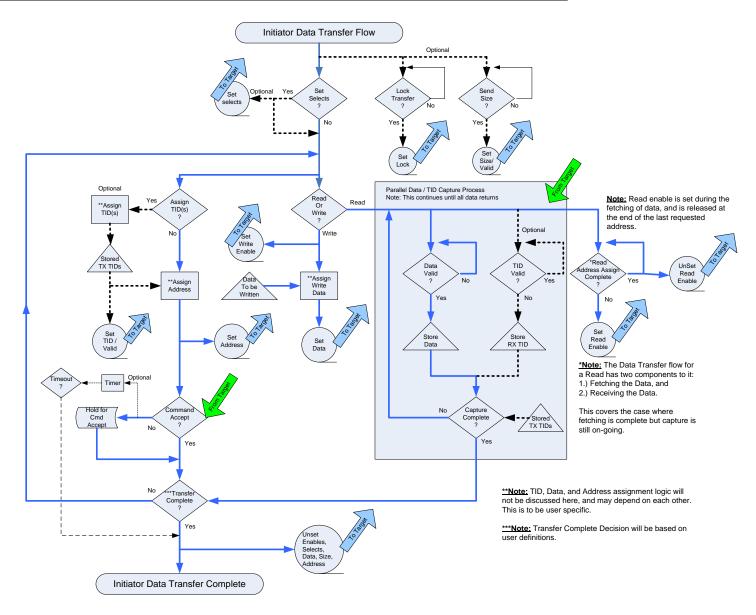

| FIGURE 14 – INITIATOR DATA AND CONTROL TRANSFER FLOW DIAGRAM | 107 |

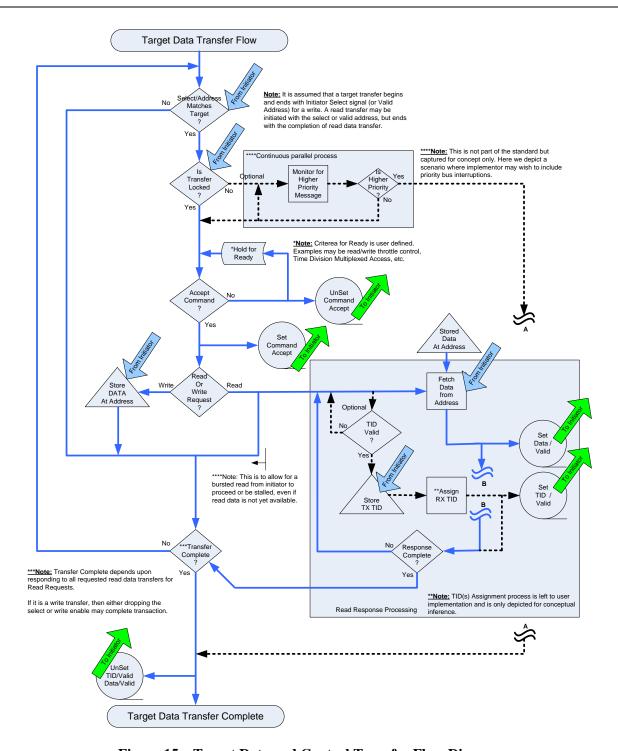

| FIGURE 15 – TARGET DATA AND CONTROL TRANSFER FLOW DIAGRAM    | 108 |

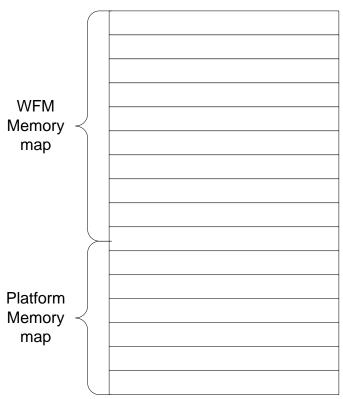

| FIGURE 16 – SINGLE FPGA MEMORY MAP                           | 110 |

| FIGURE 17 – MULTIPLE FPGA SINGLE PLATFORM MEMORY ALLOCATION  | 110 |

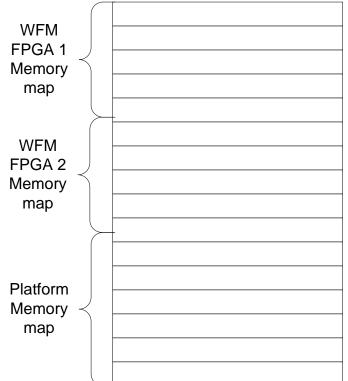

| FIGURE 18 – MULTIPLE FPGA SPLIT PLATFORM MEMORY ALLOCATION   | 111 |

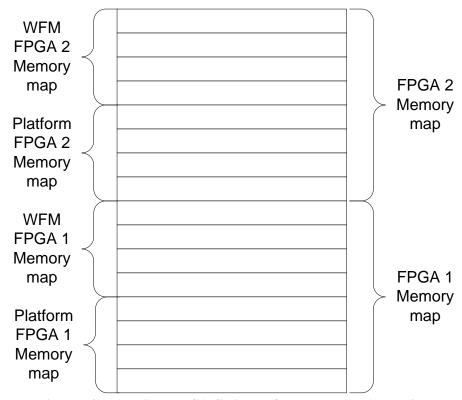

| FIGURE 19 – EXAMPLE MOCB INTERCONNECT TRANSLATION LAYER      | 118 |

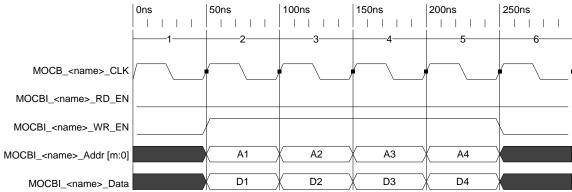

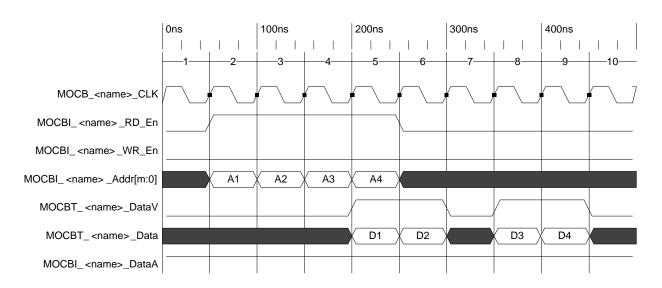

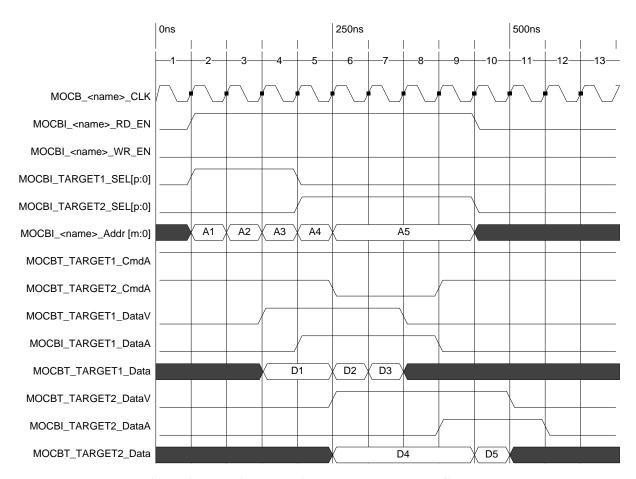

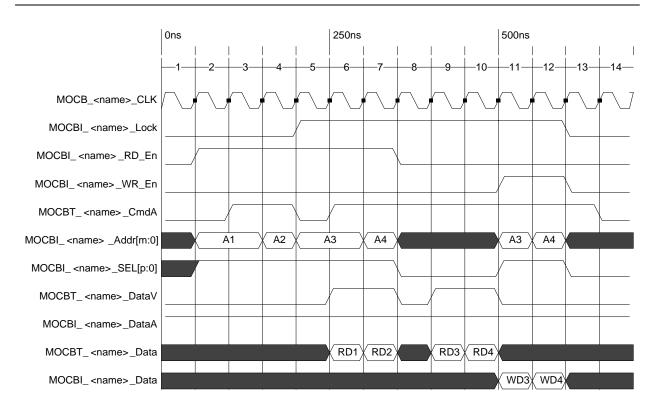

| FIGURE 20 – BASIC BURST WRITE                                | 119 |

| FIGURE 21 – BASIC BURST WRITE                                | 119 |

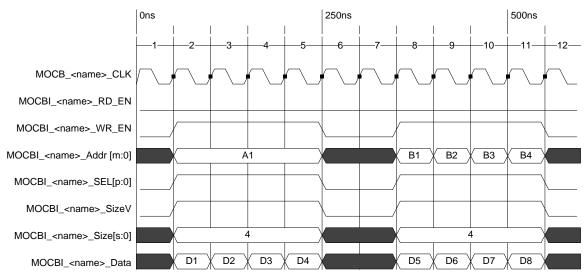

| FIGURE 22 – BASIC BURST WRITE W/SIZE                         | 120 |

| FIGURE 23 – BASIC BURST WRITE W/SIZE                         | 120 |

| FIGURE 24 – BASIC READ.                                      | 121 |

| FIGURE 25 – BASIC READ                                       | 122 |

| FIGURE 26 – BASIC READ WITH DATA ACCEPT                      | 123 |

| FIGURE 27 – BASIC READ WITH RETURN DATA FLOW CONTROL         | 124 |

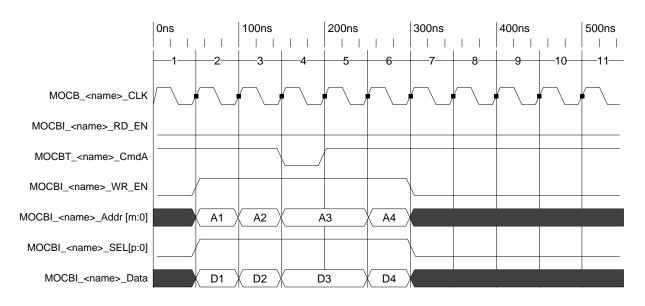

| FIGURE 28 – WRITE COMMAND WITH COMMAND FLOW CONTROL          | 125 |

| FIGURE 29 – WRITE COMMAND WITH FLOW CONTROL                  | 126 |

| FIGURE 30 – READ/WRITE WITH ACCESS CONTROL AND LOCK          | 127 |

| FIGURE 31 – READ/WRITE WITH ACCESS CONTROL AND LOCK          | 128 |

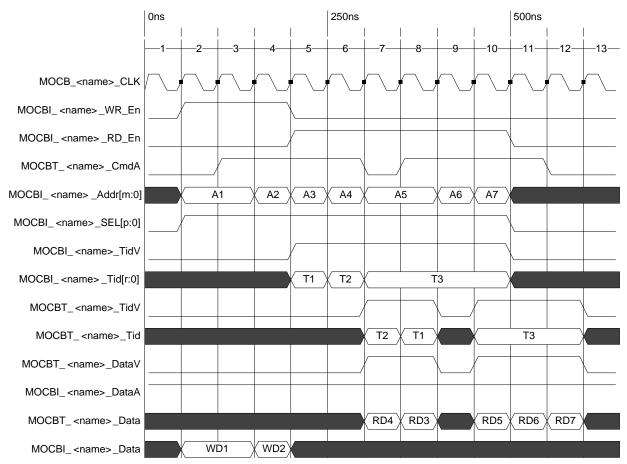

| FIGURE 32 – WRITE/READ WITH ACCESS CONTROL AND TID           | 129 |

| FIGURE 33 - WRITE/READ WITH ACCESS CONTROL AND TIDS          | 130 |

# **List of Tables**

| Table 1 – MOCB Provide Service Interface                | 21  |

|---------------------------------------------------------|-----|

| TABLE 2 – MOCB GPP EXTENSION: READ OPERATION CALLBACK   | 24  |

| TABLE 3 – MOCB GPP EXTENSION: WRITE OPERATION CALLBACK  | 31  |

| TABLE 4 – MOCB GPP EXTENSION: MODIFY OPERATION CALLBACK | 38  |

| TABLE 5 – MOCB PERFORMANCE SPECIFICATION                | 59  |

| TABLE 6 – MOCB CLOCK SPECIFICATION                      | 140 |

#### A. MOCB

#### A.1 INTRODUCTION

This API provides information to the software developer to utilize the *Modem Hardware Abstraction Layer on Chip Bus (MOCB)* interfaces in waveform target configurations.

The MOCB API provides parallel interfaces between the JTR channel modem interfaces from the application software. The MOCB API supports communications between application components hosted on General Purpose Processors (GPPs), Modem Digital Signal Processors (DSPs) and/or Modem Field Programmable Gate Arrays (FPGAs).

For the purposes of this API, the following applies to processor naming conventions:

- A GPP represents a CORBA capable processor (this could be a DSP that supports CORBA).

- A DSP represents a C capable processor, but does not provide CORBA capability.

- An FPGA represents a HDL capable processor, again without CORBA capability.

From one MHAL Computational Element (CE) (i.e. GPP, FPGA, or DSP) (see MHAL API [1]), it is possible to access other CE(s) using the interfaces defined in each MOCB API extension. The MOCB FPGA represents the parallel address/data bus interface and is the Waveform/User interface to a memory map. The MOCB FPGA consists of an FPGA entity library linked into a waveform build. The JTR set interfaces are unique, but the interfaces exposed to waveform components defined in section D MOCB FPGA API Extension. The MOCB GPP is the CORBA-based SCA CF::Device [2] interface and defined in section B MOCB GPP API Extension. The MOCB DSP is a library of standardized components linked into the waveform code at build time. The external interfaces and transport are JTR set defined, but the exposed interfaces to DSP waveform components defined in section C MOCB DSP API Extension. Additional capabilities for RF control; specifically Power Control (PC), Scanning, and Receiver Gain are defined in section E MOCB RF Chain Coordinator (RFC) API Extension.

The MOCB API does not specify the number of CEs a JTR platform provide. The MOCB API does not specify the platform specific transport, implementation or hardware architecture. For example, the MOCB API is byte oriented and abstracts away the details of the hardware architecture, like a physical interface's transfer dimensions (8/16/32/64 bits).

The MOCB API does specify the parallel interfaces of different CEs for communication between the waveform and hardware.

The MOCB GPP/DSP API (at this time) only supports the basic functionality of the MOCB FPGA API Extension. APIs for extended features such as "Locked Transfers" or "Priority Transfers will be added as required.

## A.1.1 Overview

This document contains as follows:

a. Section A.1, *Introduction*, of this document contains the introductory material regarding the Overview, Service Layer description, and Referenced Documents of this document.

- b. Section A.2, Services, provides summary of service uses.

- c. Section A.3, Interface Definitions

- d. Section A.5, Data Types and Exceptions

- e. Appendix A.A Abbreviations and Acronyms

- f. Appendix A.B Performance Specification

# **A.1.2 Service Layer Description**

Not applicable

### A.1.3 Referenced Documents

The following documents of the exact issue shown form a part of this specification to the extent specified herein.

### **A.1.3.1 Government Documents**

The following documents are part of this specification as specified herein.

## A.1.3.1.1 Specifications

#### A.1.3.1.1.1 Federal Specifications

None

#### A.1.3.1.1.2 Military Specifications

None

#### A.1.3.1.1.3 Other Government Agency Documents

- [1] JTRS Standard, "JTRS Standard MHAL API," JTNC, Version 2.13.2

- [2] JTRS Standard, "Software Communications Architecture (SCA)," JPEO, Version 2.2.2.

- [3] JTRS Standard, "JTRS Standard CORBA Types," JPEO, Version 1.0.2

- [4] JTRS Standard, "Software Communications Architecture (SCA)," JPEO, Version 4.0.

## **A.2 SERVICES**

# A.2.1 General Assumptions

- ❖ MOCB software operations provide feedback to the caller via error codes.

- ❖ MOCB software requires the Waveform provided source or destination buffer memory to be aligned matching the platform.

- ❖ MOCB software requires the Waveform provided semaphore string "name" (handle for DSP) to represent a previously registered named semaphore.

- ❖ MOCB software is byte addressable.

- ❖ MOCB SW addresses data on byte boundaries regardless of the data width.

# A.2.2 Logical Destination (LD) Assumptions

- ❖ The LD is mapped to an address in the FPGA physical memory (e.g. LD\_1, LD\_2, LD\_3)

- No size is associated with the LD to address mapping. Size is defined by the User/Waveform at the time of the call (read, write, etc.). The platform could choose to restrict/bound the size at that time.

- LDs can be mapped to any location in memory. Allowing LDs to overlap and possibly appear as subsets to another LD.

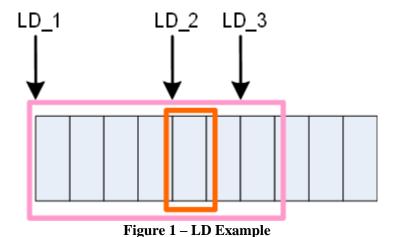

In **Figure 1**, for example, the assumptions would imply that when a "read" (**pink below**) is executed for LD\_1, other LDs (LD\_2, LD\_3) could be mapped into the memory space being read. Likewise LD\_2 could later be accessed (**orange below**) for only a subset of the previous "read" operation of LD 1.

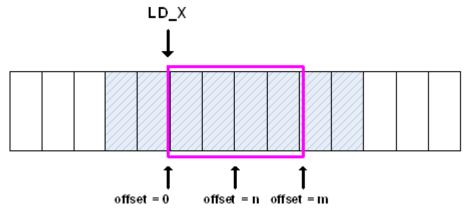

The MOCB addressing is performed with an LD and an offset within the specified LD as shown in **Figure 2**. The offset permits granular access to registers within a memory range assigned to a logical

destination. **Figure 2** shows that an offset of 0 (zero) would point to the beginning of the logical destination. Offsets n and m in the figure are address offsets within the logical destination X (LD\_X). The shaded area is the waveform memory map within the terminal memory map accessible by this operation.

Figure 2 – LD Offset Example

## **A.3 SERVICE PRIMITIVES AND ATTRIBUTES**

None

## **A.4 INTERFACE DEFINITIONS**

None

## A.5 DATA TYPES AND EXCEPTIONS

#### APPENDIX A.A – ABBREVIATIONS AND ACRONYMS

API Application Program Interface

CE Computational Element

**CF** Core Framework

CLK Clock

**CORBA** Common Object Request Broker Architecture

DMA Direct Memory AccessDSP Digital Signal Processor

**EN** Enable

**EOM** End of Message FIFO First In First Out

**FPGA** Field Programmable Gate Array

Fx Function

GPIO General Purpose Input/Output

GPP General Purpose Processor

HDL Hardware Description Language

HW Hardware I/O Input/Output

ICDInterface Control DocumentICWGInterface Control Working GroupIDLInterface Definition Language

IU In-Use (bit)

JPEO Joint Program Executive Office

JTNC Joint Tactical Networking Center

JTR Joint Tactical Radio

JTRS Joint Tactical Radio System

LSB Logical Destination

Least Significant Byte

MHz Megahertz

MOCB MHAL on Chip Bus

MSB Most Significant Byte

N/A Not Applicable

PPS Pulse Per Second

**RAM** Random Access Memory

RFC Radio Frequency Chain

**Rx** Receive

**SCA** Software Communications Architecture

**SW** Software

Tid Transaction Identification Number

Tx Transmit

**UML** Unified Modeling Language

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

WF Waveform

Version: 1.1.5 26 June 2013

# **APPENDIX A.B – PERFORMANCE SPECIFICATION**

Not applicable

#### B. MOCB GPP API EXTENSION

### **B.1 INTRODUCTION**

The *MOCB GPP* API Extension extends the *MOCB* base API (see section A) and supports methods and attributes that are specific to the General Purpose Processor (GPP) Modem Hardware (HW) device represented. This API Extension provides the ability to synchronously and asynchronously read/write/modify data to and from a service user/provider's shared memory. This API Extension also provides memory mapped interfaces that provide a read (pull) capability between components. This API Extension also includes event lines to signal to the application software that data is ready. For the purposes of this API the following applies to processor naming conventions

➤ A GPP represents a CORBA capable processor (this could be a DSP that supports CORBA).

This API Extension provides information to the software developer to utilize the *MOCB GPP* interfaces in the Waveform target configurations.

All accesses to shared memory via the *MOCB GPP* and the *MOCB DSP* are atomic to prevent data corruption (this is the responsibility of the platform). A single API operation of (read/write/modify) is defined as an access.

Note: A platform may have a 64-bit long data type (vs. 32bits) which should be considered during waveform porting

### **B.1.1 Overview**

This document contains as follows:

- a. Section B.1, *Introduction*, of this document contains the introductory material regarding the overview, and Service Layer description.

- b. Section B.2, *Services*, provides summary of service interface uses, interface for each device component, port connections, and sequence diagrams.

- c. Section B.2, Services specifies the operations provided by the *MOCB GPP*.

- d. Section B.4, *IDL*

- e. Section B.5, UML

- f. Appendix B.A Abbreviations and Acronyms

- g. Appendix B.B Performance Specification

# **B.1.2 Service Layer Description**

### **B.1.2.1 MOCB Port Connections**

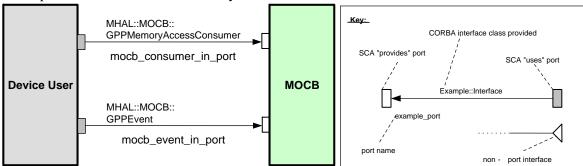

**Figure 3** shows the port connections for the *MOCB*.

Note: All port names are for reference only.

Figure 3 – MOCB Port Diagram

#### **MOCB** Provides Ports Definitions

**mocb\_consumer\_in\_port** is provided by the MOCB to synchronously and asynchronously read/write/modify data through operations available.

**mocb\_event\_in\_port** is provided by the MOCB to manage events.

#### **MOCB** Uses Ports Definitions

None

### **B.1.3 Modes of Service**

Not applicable

#### **B.1.4 Service States**

# **B.1.4.1 MOCB State Diagram**

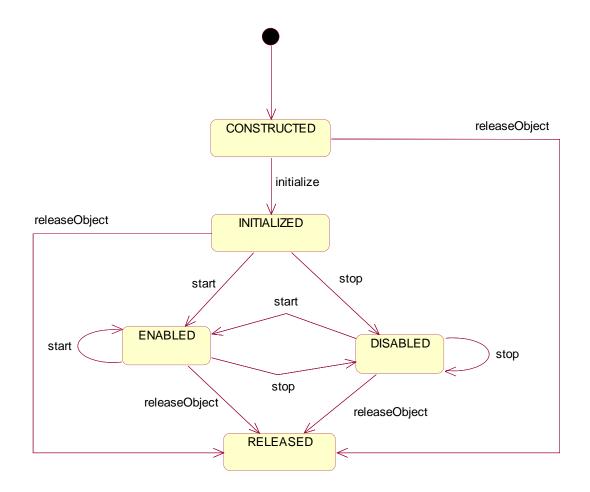

The *MOCB* state model is illustrated in **Figure 4**. *MOCB* states ensure that received operations are executed only when the *MOCB* is in the proper state. The five states of the *MOCB* are as follow:

- CONSTRUCTED The state transitioned to upon successful creation.

- INITIALIZED The state transitioned to upon successful initialization.

- ENABLED The state transitioned to upon successful start.

- DISABLED The state transitioned to upon successful stop.

- RELEASED The state transitioned to upon successful release.

The *MOCB* transitions between states in response to the initialize, start, stop and releaseObject operations.

Figure 4 – MOCB State Diagram

## **B.1.5 Referenced Documents**

The following documents of the exact issue shown form a part of this specification to the extent specified herein.

## **B.1.5.1** Government Documents

The following documents are part of this specification as specified herein.

# **B.1.5.1.1 Specifications**

B.1.5.1.1.1 Federal Specifications

None

**B.1.5.1.1.2** Military Specifications

Version: 1.1.5 26 June 2013

B.1.5.1.1.3 Other Government Agency Documents

See section A.1.3.1.1.3.

# **B.2 SERVICES**

The MOCB CORBA-compliant API separates platform interfaces from waveform interfaces.

# **B.2.1 Provide Services**

The MOCB provide service consists of the following service ports, interfaces, and primitives, which can be called by other client components.

**Table 1 – MOCB Provide Service Interface**

| Service Group (Port<br>Name) | Service (Interface Provided)            | Primitives (Provided) | Parameter Name or<br>Return Value | Valid Range          |

|------------------------------|-----------------------------------------|-----------------------|-----------------------------------|----------------------|

| mocb_consumer_in_port        | MHAL::MOCB::GPPMemory<br>AccessConsumer | read                  | See section B.3.1.1               | See section B.3.1.1  |

|                              |                                         | readWait              | See section B.3.1.2               | See section B.3.1.2  |

|                              |                                         | multiReadWait         | See section B.3.1.3               | See section B.3.1.3  |

|                              |                                         | multiLDReadWait       | See section B.3.1.4               | See section B.3.1.4  |

|                              |                                         | write                 | See section B.3.1.5               | See section B.3.1.5  |

|                              |                                         | writeWait             | See section B.3.1.6               | See section B.3.1.6  |

|                              |                                         | multiWriteWait        | See section B.3.1.7               | See section B.3.1.7  |

|                              |                                         | multiLDWriteWait      | See section B.3.1.8               | See section B.3.1.8  |

|                              |                                         | modify                | See section B.3.1.9               | See section B.3.1.9  |

|                              |                                         | modifyWait            | See section B.3.1.10              | See section B.3.1.10 |

| Service Group (Port<br>Name) | Service (Interface Provided) | Primitives (Provided) | Parameter Name or<br>Return Value | Valid Range          |

|------------------------------|------------------------------|-----------------------|-----------------------------------|----------------------|

|                              |                              | configLDMap           | See section B.3.1.11              | See section B.3.1.11 |

| mocb_event_in_port           | MHAL::MOCB::GPPEvent         | registerSemaphore     | See section B.3.2                 | See section B.3.2    |

|                              |                              | unregisterSemaphore   | See section B.3.2.2               | See section B.3.2.2  |

|                              |                              | registerEventMux      | See section B.3.2.3               | See section B.3.2.3  |

# **B.2.2** Use Services

#### **B.2.3 Interface Modules**

#### B.2.3.1 MHAL::MOCB

Figure 5 – MOCB Interface Class Diagram

# **B.2.3.1.1 GPPMemoryAccessConsumer Interface Description**

The interface of the *GPPMemoryAccessConsumer* is depicted in **Figure 5**. It provides the ability to synchronously and asynchronously read/write/modify data to and from a service user/provider's shared memory.

# **B.2.3.1.2** GPPEvent Interface Description

The interface design of the *GPPEvent* illustrated in **Figure 5** provides the ability to manage events.

# **B.2.4 Sequence Diagrams**

### **B.3 SERVICE PRIMITIVES AND ATTRIBUTES**

To enhance the readability of this API document and to avoid duplication of data, the type definitions of all structured types (i.e., structures, typedefs, exceptions, and enumerations) used by the Service Primitives and Attributes have been co-located in section B.5 UML.

# **B.3.1 MHAL::MOCB::GPPMemoryAccessConsumer**

# **B.3.1.1** read Operation

This operation provides the ability to read data from shared memory. This operation is non-blocking and returns the data via an MHAL message (**Table 2**) to the provided "callbackLD". This utilizes the *MHALPacketConsumer* interface defined in the MHAL GPP API Extension [1].

To read 32 bits, 4 octets will be used. For example, for a terminal with a 32-bit bus, the 4 octets will be used in one transaction, for a terminal with a 16-bit bus, 2 transactions will occur each using 2 octets.

Note: The callback message (10 bytes) consists of an MHAL header with the callbackLD, a payload of 6 bytes representing the ErrorCodes for this operation and the data read.

Table 2 – MOCB GPP Extension: Read Operation Callback

|   | <mhal header<="" th=""><th>&gt;</th><th><payload< th=""><th>&gt;</th></payload<></th></mhal> | >                        | <payload< th=""><th>&gt;</th></payload<> | >                          |

|---|----------------------------------------------------------------------------------------------|--------------------------|------------------------------------------|----------------------------|

| l | LD                                                                                           | Length                   |                                          |                            |

|   | callbackLD <sub>16</sub>                                                                     | nByte + 10 <sub>16</sub> | ErrorCode 32                             | Read Data <sub>nByte</sub> |

# **B.3.1.1.1** Synopsis

```

oneway void read (

in unsigned short LD,

in unsigned long offset,

in unsigned short nByte,

in unsigned short callbackLD

);

```

#### **B.3.1.1.2** Parameters

| Parameter | Description               | Type           | Units       | Valid Range   |

|-----------|---------------------------|----------------|-------------|---------------|

| Name      |                           |                |             |               |

| LD        | The logical destination   | unsigned short | Logical     | 0 - 32767     |

|           | for the message.          |                | Destination |               |

|           |                           |                | ID          |               |

| offset    | Address offset from base  | unsigned long  | Offset from | Not Specified |

|           | address assigned to a     |                | Logical     |               |

|           | logical destination (LD). |                | Destination |               |

| nByte     | The number of bytes to    | unsigned short | N/A         | 0 - 65525     |

|           | be read.                  |                |             |               |

| Parameter  | Description               | Type           | Units       | Valid Range |

|------------|---------------------------|----------------|-------------|-------------|

| Name       |                           |                |             |             |

| callbackLD | The logical destination   | unsigned short | Logical     | 0 - 32767   |

|            | for the callback message. |                | Destination |             |

|            |                           |                | ID          |             |

## **B.3.1.1.3** State

ENABLED CF::Device::operationalState.

## **B.3.1.1.4** New State

This operation does not cause a state change.

## **B.3.1.1.5 Return Value**

None

# **B.3.1.1.6** Originator

Service Provider

# **B.3.1.1.7** Exceptions

### **B.3.1.2** readWait Operation

This is a blocking operation and permits reading data from the application memory map. The user/waveform is responsible for destroying the sequence allocated during the readWait() call by the MOCB.

Note: Zero for both sec and nsec would indicate to wait indefinitely.

## **B.3.1.2.1** Synopsis

```

ErrorCodes readWait (

in unsigned long sec,

in unsigned long nsec,

in unsigned short LD,

in unsigned long offset,

in unsigned short nByte,

out JTRS::OctetSequence buf

);

```

### **B.3.1.2.2** Parameters

| Parameter | Description                                                              | Type                                                 | Units                                 | Valid Range     |

|-----------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|-----------------|

| Name      |                                                                          |                                                      |                                       |                 |

| sec       | Integer seconds of time to wait.                                         | unsigned long                                        | Seconds                               | 0 to 2147483647 |

| nsec      | Nanoseconds of time to wait.                                             | unsigned long                                        | Nanoseconds                           | 0 to 99999999   |

| LD        | Logical destination of the message.                                      | unsigned short                                       | Logical<br>Destination ID             | 0 – 32767       |

| offset    | Address offset from base address assigned to a logical destination (LD). | unsigned long                                        | Offset from<br>Logical<br>Destination | Not Specified   |

| nByte     | Number of bytes to read.                                                 | unsigned short                                       | N/A                                   | 0 – 65531       |

| buf       | The returned data.                                                       | JTRS::OctetSequence<br>(See JTRS CORBA<br>Types [3]) | N/A                                   | N/A             |

#### **B.3.1.2.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.2.4** New State

This operation does not cause a state change.

**B.3.1.2.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

# **B.3.1.2.6** Originator

Service Provider

# **B.3.1.2.7** Exceptions

### **B.3.1.3** *multiReadWait* Operation

This operation provides the ability for the application to read data from offsets within the same logical destination

## **B.3.1.3.1** Synopsis

```

ErrorCodes multiReadWait (

in unsigned long sec,

in unsigned long nsec,

in unsigned short LD,

in MultiRead addrList,

out JTRS::OctetSequence buf

);

```

# **B.3.1.3.2** Parameters

| Parameter | Description                                       | Type                                                 | Units                     | Valid Range     |

|-----------|---------------------------------------------------|------------------------------------------------------|---------------------------|-----------------|

| Name      |                                                   |                                                      |                           |                 |

| sec       | Integer seconds of time to wait.                  | unsigned long                                        | Seconds                   | 0 to 2147483647 |

| nsec      | Nanoseconds of time to wait.                      | unsigned long                                        | Nanoseconds               | 0 to 999999999  |

| LD        | Logical destination of the message.               | unsigned short                                       | Logical<br>Destination ID | 0 – 32767       |

| addrList  | Sequence of offsets, and number of bytes to read. | MultiRead (See section B.5.1.1)                      | N/A                       | N/A             |

| buf       | Returned data.                                    | JTRS::OctetSequence<br>(See JTRS CORBA<br>Types [3]) | N/A                       | N/A             |

#### **B.3.1.3.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.3.4** New State

This operation does not cause a state change.

#### **B.3.1.3.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

# **B.3.1.3.6** Originator

Service Provider.

Version: 1.1.5 26 June 2013

# **B.3.1.3.7** Exceptions

### B.3.1.4 multiLDReadWait Operation

This operation provides the ability for the application to read data from offsets from multiple logical destinations.

## **B.3.1.4.1** Synopsis

```

ErrorCodes multiLDReadWait (

in unsigned long sec,

in unsigned long nsec,

in MultiLDRead addrList,

out JTRS::OctetSequence buf

);

```

#### **B.3.1.4.2** Parameters

| Parameter | Description         | Туре                  | Units       | Valid Range     |

|-----------|---------------------|-----------------------|-------------|-----------------|

| Name      |                     |                       |             |                 |

| sec       | Integer seconds to  | unsigned long         | Seconds     | 0 to 2147483647 |

|           | wait.               |                       |             |                 |

| nsec      | Nanoseconds of      | unsigned long         | Nanoseconds | 0 to 999999999  |

|           | time to wait.       |                       |             |                 |

| addrList  | A sequence of LDs,  | MultiLDRead           | N/A         | N/A             |

|           | offsets, and number | (See section B.5.1.2) |             |                 |

|           | of bytes to read.   |                       |             |                 |

| buf       | The data read.      | JTRS::OctetSequence   | N/A         | N/A             |

|           |                     | (See JTRS CORBA       |             |                 |

|           |                     | Types [3])            |             |                 |

#### **B.3.1.4.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.4.4** New State

This operation does not cause a state change.

#### **B.3.1.4.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

# **B.3.1.4.6** Originator

Service Provider.

# **B.3.1.4.7** Exceptions

### **B.3.1.5** *write* Operation

This operation writes data to shared memory. The operation is non-blocking and returns a confirmation via an MHAL message (**Table 3**) to the provided "callbackLD". This utilizes the *MHALPacketConsumer* interface defined in the MHAL GPP API Extension [1].

Four octets are used to write 32 bits. As an example, a terminal with a 32-bit bus will transmit 4 octets one transaction, whereas a terminal with a 16-bit bus will execute 2 transactions with 2 octets each.

A "non-blocking" write() with a "callbackLD" of "NOCALLBACK" disables the confirmation callback for that instance. "NOCALLBACK" is defined as a symbolic LD reference just like "RFCHAIN" and is assigned a value by the platform.

Note: The callback message (8 bytes) consists of an MHAL header with the callbackLD and a payload of 4 bytes containing the ErrorCodes for this operation.

Table 3 - MOCB GPP Extension: Write Operation Callback

| <mhal header<="" th=""><th>&gt;</th><th><payload< th=""><th>&gt;</th></payload<></th></mhal> | >                      | <payload< th=""><th>&gt;</th></payload<> | > |

|----------------------------------------------------------------------------------------------|------------------------|------------------------------------------|---|

| LD                                                                                           | Length                 |                                          |   |

| callbackLD <sub>16</sub>                                                                     | <b>8</b> <sub>16</sub> | ErrorCode 32                             |   |

## **B.3.1.5.1** Synopsis

```

oneway void write (

in unsigned short LD,

in unsigned long offset,

in JTRS::OctetSequence buf,

in unsigned short callbackLD

);

```

#### **B.3.1.5.2** Parameters

| Parameter<br>Name | Description                                                              | Туре           | Units                                 | Valid Range   |

|-------------------|--------------------------------------------------------------------------|----------------|---------------------------------------|---------------|

| LD                | Logical destination for the message                                      | unsigned short | Logical<br>Destination<br>ID          | 0 – 32767     |

| offset            | Address offset from base address assigned to a logical destination (LD). | unsigned long  | Offset from<br>Logical<br>Destination | Not Specified |

Units Valid Range Parameter **Description** Type Name The data to be written. JTRS::OctetSequence N/A N/A buf (See JTRS CORBA Note: The length of Types [3]) the sequence is used as the size of the transaction. callbackLD The logical unsigned short Logical 0 - 32767destination for the Destination callback message ID

#### **B.3.1.5.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.5.4** New State

This operation does not cause a state change.

#### **B.3.1.5.5** Return Value

None

## **B.3.1.5.6** Originator

Service Provider

# **B.3.1.5.7** Exceptions

## **B.3.1.6** write Wait Operation

This operation is blocking and provides the ability to write data to shared memory.

Note: Zero for both sec and nsec indicates to wait indefinitely.

## **B.3.1.6.1** Synopsis

```

ErrorCodes writeWait (

in unsigned long sec,

in unsigned long nsec,

in unsigned short LD,

in unsigned long offset,

in JTRS::OctetSequence buf

);

```

### **B.3.1.6.2** Parameters

| Parameter<br>Name | Description                                                                                       | Туре                                                 | Units                                 | Valid Range     |

|-------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|-----------------|

| sec               | Integer seconds of time to wait.                                                                  | unsigned long                                        | Seconds                               | 0 to 2147483647 |

| nsec              | Nanoseconds of time to wait.                                                                      | unsigned long                                        | Nanoseconds                           | 0 to 99999999   |

| LD                | The logical destination for the message                                                           | unsigned short                                       | Logical<br>Destination ID             | 0 – 32767       |

| offset            | Address offset from base address assigned to a logical destination (LD).                          | unsigned long                                        | Offset from<br>Logical<br>Destination | Not Specified   |

| buf               | The data to be written.  Note: The length of the sequence is used as the size of the transaction. | JTRS::OctetSequence<br>(See JTRS CORBA<br>Types [3]) | N/A                                   | N/A             |

## **B.3.1.6.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.6.4** New State

This operation does not cause a state change.

# **B.3.1.6.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

# **B.3.1.6.6** Originator

Service Provider

# **B.3.1.6.7** Exceptions

## **B.3.1.7** *multiWriteWait* Operation

This operation provides the ability for the application to write data to offsets within same logical destination.

## **B.3.1.7.1** Synopsis

```

ErrorCodes multiWriteWait (

in unsigned long sec,

in unsigned long nsec,

in unsigned short LD,

in MultiWrite addrValPairs

);

```

#### **B.3.1.7.2** Parameters

| Parameter    | Description           | Type                  | Units          | Valid Range     |

|--------------|-----------------------|-----------------------|----------------|-----------------|

| Name         |                       |                       |                |                 |

| sec          | Integer seconds of    | unsigned long         | Seconds        | 0 to 2147483647 |

|              | time to wait.         |                       |                |                 |

| nsec         | Nanoseconds of        | unsigned long         | Nanoseconds    | 0 to 99999999   |

|              | time to wait.         |                       |                |                 |

| LD           | The logical           | unsigned short        | Logical        | 0 - 32767       |

|              | destination for the   |                       | Destination ID |                 |

|              | message.              |                       |                |                 |

| addrValPairs | A sequence of         | MultiWrite            | N/A            | N/A             |

|              | offsets, and the      | (See section B.5.1.3) |                |                 |

|              | buffers of data to be |                       |                |                 |

|              | written.              |                       |                |                 |

### **B.3.1.7.3** State

$ENABLED\ CF:: Device:: operational State.$

#### **B.3.1.7.4** New State

This operation does not cause a state change.

#### **B.3.1.7.5 Return Value**

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

# **B.3.1.7.6 Originator**

Service Provider.

Version: 1.1.5 26 June 2013

# **B.3.1.7.7** Exceptions

### B.3.1.8 multiLDWriteWait Operation

This operation provides the ability for the application to write data to offsets within multiple logical destinations.

## **B.3.1.8.1** Synopsis

```

ErrorCodes multiLDWriteWait (

in unsigned long sec,

in unsigned long nsec,

in MultiLDWrite addrValPairs

);

```

### **B.3.1.8.2** Parameters

| Parameter<br>Name | Description                                                        | Type                                  | Units       | Valid Range     |

|-------------------|--------------------------------------------------------------------|---------------------------------------|-------------|-----------------|

| sec               | Integer seconds of time to wait.                                   | unsigned long                         | Seconds     | 0 to 2147483647 |

| nsec              | Nanoseconds of time to wait.                                       | unsigned long                         | Nanoseconds | 0 to 99999999   |

| addrValPairs      | A sequence of LDs, offsets, and the buffers of data to be written. | MultiLDWrite<br>(See section B.5.4.4) | N/A         | N/A             |

### **B.3.1.8.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.8.4** New State

This operation does not cause a state change.

#### **B.3.1.8.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.1.8.6** Originator

Service Provider

## **B.3.1.8.7** Exceptions

### **B.3.1.9** *modify* Operation

This operation modifies data in shared memory. The operation is non-blocking and returns a confirmation via an MHAL message to the provided "callbackLD". This utilizes the *MHALPacketConsumer* interface defined in the MHAL GPP API Extension [1].

Four octets are used to write 32 bits. As an example, a terminal with a 32-bit bus will transmit 4 octets one transaction, whereas a terminal with a 16-bit bus will execute 2 transactions with 2 octets each.

A modify() with a "callbackLD" of NOCALLBACK disables the confirmation callback for that instance. NOCALLBACK is defined as a symbolic LD reference just like RFCHAIN and is assigned a value by the platform.

Note: The callback message (8 bytes) consists of an MHAL header with the callbackLD and a payload of 4 bytes representing the ErrorCodes for this operation.

Table 4 – MOCB GPP Extension: Modify Operation Callback

| <mhal header<="" th=""><th>&gt;</th><th><payload< th=""><th>&gt;</th></payload<></th></mhal> | >                      | <payload< th=""><th>&gt;</th></payload<> | > |

|----------------------------------------------------------------------------------------------|------------------------|------------------------------------------|---|

| LD                                                                                           | Length                 |                                          |   |

| callbackLD <sub>16</sub>                                                                     | <b>8</b> <sub>16</sub> | ErrorCode 32                             |   |

### **B.3.1.9.1** Synopsis

```

oneway void modify (

in unsigned short LD,

in unsigned long offset,

in JTRS::OctetSequence buf,

in BitOp bitOperation,

in unsigned short callbackLD

);

```

#### **B.3.1.9.2** Parameters

| Parameter | Description              | Type           | Units       | Valid Range   |

|-----------|--------------------------|----------------|-------------|---------------|

| Name      |                          |                |             |               |

| LD        | The logical              | unsigned short | Logical     | 0 - 32767     |

|           | destination for the      |                | Destination |               |

|           | message                  |                | ID          |               |

| offset    | Address offset from      | unsigned long  | Offset from | Not Specified |

|           | base address assigned    |                | Logical     |               |

|           | to a logical destination |                | Destination |               |

|           | (LD).                    |                |             |               |

Valid Range Parameter **Description** Type Units Name The data to be JTRS::OctetSequence N/A N/A buf modified. (See JTRS CORBA Types [3]) Note: The length of the sequence is used as the size of the transaction. The bitwise operation bitOperation BitOp N/A See section B.5.2.3 to be performed. callbackLD The logical unsigned short Logical 0 - 32767destination for the Destination callback message ID

### **B.3.1.9.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.9.4** New State

This operation does not cause a state change.

### **B.3.1.9.5 Return Value**

None

## **B.3.1.9.6** Originator

Service Provider

## **B.3.1.9.7 Exceptions**

### B.3.1.10 modify Wait Operation

This operation is blocking and provides the ability to modify data in shared memory.

Note: Zero for both sec and nsec indicate to wait indefinitely.

## **B.3.1.10.1** Synopsis

```

ErrorCodes modifyWait (

in unsigned long sec,

in unsigned long nsec,

in unsigned short LD,

in unsigned long offset,

in JTRS::OctetSequence buf,

in BitOp bitOperation

);

```

### **B.3.1.10.2** Parameters

| Parameter    | Description         | Type                | Units          | Valid Range         |

|--------------|---------------------|---------------------|----------------|---------------------|

| Name         |                     |                     |                |                     |

| sec          | Integer seconds of  | unsigned long       | Seconds        | 0 to 2147483647     |

|              | time to wait.       |                     |                |                     |

| nsec         | Nanoseconds of      | unsigned long       | Nanoseconds    | 0 to 999999999      |

|              | time to wait.       |                     |                |                     |

| LD           | The logical         | unsigned short      | Logical        | 0 - 32767           |

|              | destination for the |                     | Destination ID |                     |

|              | message             |                     |                |                     |

| offset       | Address offset      | unsigned long       | Offset from    | Not Specified       |

|              | from base address   |                     | Logical        |                     |

|              | assigned to a       |                     | Destination    |                     |

|              | logical destination |                     |                |                     |

|              | (LD).               |                     |                |                     |

| buf          | The data to be      | JTRS::OctetSequence | N/A            | N/A                 |

|              | operated on.        | (See JTRS CORBA     |                |                     |

|              |                     | Types [3])          |                |                     |

|              | Note: The length of |                     |                |                     |

|              | the sequence is     |                     |                |                     |

|              | used as the size of |                     |                |                     |

|              | the transaction.    |                     |                |                     |

| bitOperation | The bitwise         | BitOp               | N/A            | See section B.5.2.3 |

|              | operation to be     |                     |                |                     |

|              | performed.          |                     |                |                     |

### **B.3.1.10.3** State

ENABLED CF::Device::operationalState.

Version: 1.1.5 26 June 2013

### **B.3.1.10.4** New State

This operation does not cause a state change.

## **B.3.1.10.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.1.10.6** Originator

Service Provider

## **B.3.1.10.7** Exceptions

### B.3.1.11 configLDMap Operation

This operation maps logical destinations to a starting address in the waveform memory map. The terminal software has knowledge of which portion of its memory map are for the waveform.

The "addressWidth" is used to determine the space reserved for the address component of the LD & Address pair in the payload parameter.

## **B.3.1.11.1** Synopsis

```

ErrorCodes configLDMap (

in Map configMap

);

```

### **B.3.1.11.2** Parameters

| Parameter<br>Name | Description                 | Type | Units | Valid Range         |

|-------------------|-----------------------------|------|-------|---------------------|

| configMap         | Mapping of LDs to addresses | Map  | N/A   | See section B.5.1.1 |

#### **B.3.1.11.3** State

ENABLED CF::Device::operationalState.

#### **B.3.1.11.4** New State

This operation does not cause a state change.

#### **B.3.1.11.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.1.11.6** Originator

Service Provider

## **B.3.1.11.7 Exceptions**

### **B.3.2 MHAL::MOCB::GPPEvent**

### B.3.2.1 registerSemaphore Operation

This operation registers a semaphore managed (created and destroyed) by the waveform software. The waveform calls this operation for each relevant subEvent represented by a bit in the event mux register\*\*.

The semaphore is posted by the MOCB software when the specified MOCB event occurs. This event is known by the waveform software and the waveform firmware (e.g., an FPGA event line). The waveform hardware event line(s) is(are) mapped to terminal specific hardware (e.g., a GPIO line(s)) during waveform porting. The terminal software has knowledge of which terminal lines are connected to waveform hardware lines, and upon assertion of that discrete, the semaphore is posted.

The MOCB software provides event triggering to waveform software on a per bit basis within the event mux register.

The waveform firmware is responsible to clear all the subEvent bit(s) in the mux register after detecting the MOCB software reading the mux register (if more synchronization controls are required, the waveform may implement an independent clear/feedback register that can be written by waveform software via the MOCB *write*() or *writeWait*() operations)

MOCB software will post all subEvents present when the mux register is read after the MOCB event line is signaled.

\*\* Note: The MOCB firmware provides a minimum of (1...n) event line(s) for waveform use. The waveform firmware provides one event mux register(1...n bytes) for each MOCB event line.

## **B.3.2.1.1** Synopsis

```

ErrorCodes registerSemaphore (

in unsigned short eventId,

in unsigned short subEventId,

in string name

);

```

### **B.3.2.1.2** Parameters

| Parameter | Description                                                                                                                                | Type           | Units | Valid Range |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|-------------|

| Name      |                                                                                                                                            |                |       |             |

| eventId   | The event Identifier associated with the semaphore.  This represents the event provided to waveform software from the MOCB FPGA interface. | unsigned short | N/A   | 0 – 32767   |

| Parameter<br>Name | Description                                                             | Туре           | Units | Valid Range |

|-------------------|-------------------------------------------------------------------------|----------------|-------|-------------|

| subEventId        | Associated with the bit position in the waveform provided mux register. | unsigned short | N/A   | 0 – 32767   |

| name              | Name of the semaphore created by the application                        | string         | N/A   | N/A         |

## **B.3.2.1.3** State

ENABLED CF::Device::operationalState.

### **B.3.2.1.4** New State

This operation does not cause a state change.

## **B.3.2.1.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.2.1.6 Originator**

Service Provider

## **B.3.2.1.7** Exceptions

### **B.3.2.2** unregisterSemaphore Operation

Un-registers a previously registered semaphore upon a MOCB event. The only parameter needed to unregister a semaphore is the name.

## **B.3.2.2.1** Synopsis

```

ErrorCodes unregisterSemaphore (

in string name

);

```

### **B.3.2.2.2** Parameters

| Parameter | Description          | Type   | Units | Valid Range |

|-----------|----------------------|--------|-------|-------------|

| Name      |                      |        |       |             |

| name      | Name of the          | string | N/A   | N/A         |

|           | semaphore created by |        |       |             |

|           | the application      |        |       |             |

#### **B.3.2.2.3** State

ENABLED CF::Device::operationalState.

### **B.3.2.2.4** New State

This operation does not cause a state change.

### **B.3.2.2.5 Return Value**

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.2.2.6** Originator

Service Provider

## **B.3.2.2.7 Exceptions**

## B.3.2.3 registerEventMux Operation

This operation assigns an event to a mux register of subEvents the waveform will use. The waveform calls this operation on each MOCB event line.

## **B.3.2.3.1** Synopsis

```

ErrorCodes registerEventMux(

in unsigned short eventId,

in unsigned short LD,

in unsigned long offset,

in unsigned short nByte

):

```

### **B.3.2.3.2** Parameters

| Parameter | Description                                                                                                                                                               | Туре           | Units                                 | Valid Range   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------|---------------|

| eventId   | The event Identifier that represents the event discrete provided to waveform software from the MOCB FPGA interface (i.e. MOCB firmware)                                   | unsigned short | N/A                                   | 0 – 32767     |

| LD        | The logical destination for the message.  This is the location in the waveform memory space where the platform reads "nbytes" of event mux register when "eventId" occurs | unsigned short | Logical<br>Destination<br>ID          | 0 – 32767     |

| offset    | Address offset from base address assigned to a logical destination (LD).                                                                                                  | unsigned long  | Offset from<br>Logical<br>Destination | Not Specified |

| nByte     | The number of bytes to be read.                                                                                                                                           | unsigned short | N/A                                   | 0 – 65525     |

### **B.3.2.3.3** State

ENABLED CF::Device::operationalState.

Version: 1.1.5 26 June 2013

### **B.3.2.3.4** New State

This operation does not cause a state change.

## **B.3.2.3.5** Return Value

| Description                            | Type       | Units | Valid Range |

|----------------------------------------|------------|-------|-------------|

| The error code representing the status | ErrorCodes | N/A   | See section |

| of the operation's completion          |            |       | B.5.2.2     |

## **B.3.2.3.6** Originator

Service Provider

## **B.3.2.3.7** Exceptions

### **B.4 IDL**

### **B.4.1 MOCB Device IDL**

```

** MocbDevice.idl

#ifndef __MOCBDEVICE_DEFINED

#define __MOCBDEVICE_DEFINED

#ifndef JTRSCORBATYPES DEFINED

#include "JtrsCorbaTypes.idl"

#endif

module MHAL {

module MOCB {

struct MultiLDReadEntry {

unsigned short LD;

unsigned long offset;

unsigned short nByte;

};

typedef sequence<MultiLDReadEntry> MultiLDRead;

struct MultiReadEntry {

unsigned long offset;

unsigned short nByte;

};

typedef sequence<MultiReadEntry> MultiRead;

struct MultiLDWriteEntry {

unsigned short LD;

unsigned long offset;

JTRS::OctetSequence buf;

};

typedef sequence<MultiLDWriteEntry> MultiLDWrite;

struct MultiWriteEntry {

unsigned long offset;

JTRS::OctetSequence buf;

};

typedef sequence<MultiWriteEntry> MultiWrite;

typedef JTRS::ExtEnum AddressIndexType;

const AddressIndexType CONSTANT = 0;

const AddressIndexType INCREMENT= 1;

const AddressIndexType DECREMENT = 2;

typedef short ErrorCodes;

```

```

const ErrorCodes SUCCESSFUL = 0;

const ErrorCodes INV MEM ACCESS = -1;

const ErrorCodes INV LD \overline{OR} ADDR = -2;

const ErrorCodes SRC MEM NOT ALIGNED = -3;

const ErrorCodes DST MEM NOT ALIGNED = -4;

const ErrorCodes INV EVENT ID = -5;

const ErrorCodes INV SEMAPHORE NAME = -6;

const ErrorCodes INV TIME = -7;

const ErrorCodes INV SUBEVENT = -8;

const ErrorCodes TIMER EXPIRED = -9;